# **MITSUBISHI**

# Type ACPU/QCPU-A (A Mode)

Programming Manual (Common Instructions)

## ● SAFETY CAUTIONS ●

(You must read these cautions before using the product)

In connection with the use of this product, in addition to carefully reading both this manual and the related manuals indicated in this manual, it is also essential to pay due attention to safety and handle the product correctly.

The safety cautions given here apply to this product in isolation. For information on the safety of the PC system as a whole, refer to the CPU module User's Manual.

Store this manual carefully in a place where it is accessible for reference whenever necessary, and forward a copy of the manual to the end user.

## CONDITIONS OF USE FOR THE PRODUCT

- (1) Mitsubishi programmable controller ("the PRODUCT") shall be used in conditions;

- i) where any problem, fault or failure occurring in the PRODUCT, if any, shall not lead to any major or serious accident; and

- ii) where the backup and fail-safe function are systematically or automatically provided outside of the PRODUCT for the case of any problem, fault or failure occurring in the PRODUCT.

- (2) The PRODUCT has been designed and manufactured for the purpose of being used in general industries.

MITSUBISHI SHALL HAVE NO RESPONSIBILITY OR LIABILITY (INCLUDING, BUT NOT LIMITED TO ANY AND ALL RESPONSIBILITY OR LIABILITY BASED ON CONTRACT, WARRANTY, TORT, PRODUCT LIABILITY) FOR ANY INJURY OR DEATH TO PERSONS OR LOSS OR DAMAGE TO PROPERTY CAUSED BY the PRODUCT THAT ARE OPERATED OR USED IN APPLICATION NOT INTENDED OR EXCLUDED BY INSTRUCTIONS, PRECAUTIONS, OR WARNING CONTAINED IN MITSUBISHI'S USER, INSTRUCTION AND/OR SAFETY MANUALS, TECHNICAL BULLETINS AND GUIDELINES FOR the PRODUCT.

("Prohibited Application")

Prohibited Applications include, but not limited to, the use of the PRODUCT in;

- Nuclear Power Plants and any other power plants operated by Power companies, and/or any other cases in which the public could be affected if any problem or fault occurs in the PRODUCT.

- Railway companies or Public service purposes, and/or any other cases in which establishment of a special quality assurance system is required by the Purchaser or End User.

- Aircraft or Aerospace, Medical applications, Train equipment, transport equipment such as Elevator and Escalator, Incineration and Fuel devices, Vehicles, Manned transportation, Equipment for Recreation and Amusement, and Safety devices, handling of Nuclear or Hazardous Materials or Chemicals, Mining and Drilling, and/or other applications where there is a significant risk of injury to the public or property.

Notwithstanding the above, restrictions Mitsubishi may in its sole discretion, authorize use of the PRODUCT in one or more of the Prohibited Applications, provided that the usage of the PRODUCT is limited only for the specific applications agreed to by Mitsubishi and provided further that no special quality assurance or fail-safe, redundant or other safety features which exceed the general specifications of the PRODUCTs are required. For details, please contact the Mitsubishi representative in your region.

## **REVISIONS**

\*The manual number is given on the bottom left of the back cover.

| Print Date | *Manual Number  | Revision                                                                                                                                                                             |

|------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Oct., 1990 | IB (NA) 66250-A | First edition                                                                                                                                                                        |

| Aug., 1993 | IB (NA) 66250-B | Descriptions of AnUCPU, A52GCPU, and A1SCPU are added. "Subset" and "Number of steps" in the Available Device in Sections 5 to 7 are deleted.                                        |

| May, 1998  | IB (NA) 66250-C | Addition of Models                                                                                                                                                                   |

|            |                 | A1SCPU-S1, A1SJCPU, A1SJCPU-S3, A1SCPUC24-R2, A2SCPU, A2SCPU-S1, A1SHCPU, A1SJHCPU, A2SHCPU, A2SHCPU-S1, A2ASCPU, A2ASCPU-S1, A2ASCPU-S30, A2ASCPU-S60, A2CCPU-S3, A1FXCPU  Addition |

|            |                 | Section 7.6.5, 7.6.6, 8.3.3                                                                                                                                                          |

|            |                 | Correction                                                                                                                                                                           |

|            |                 | SAFETY PRECAUTIONS, CONTENTS, Section 2.1, 2.2.3, 3.1, 3.4, 6.4.3, 6.5.2, 6.6.1, 7.4.6, 7.6.1, 7.9.1, 7.10.2, 8.3.4, 9.2, 9.3, 9.4, APP 1.3, APP 2                                   |

|            |                 | Deletion                                                                                                                                                                             |

|            |                 | A2NCPU(P21/R21)-F, A2NCPU(P21/R21)-S1-F,<br>A3NCPU(P21/R21)-F, A373CPU(P21/R21)                                                                                                      |

| Jan., 2000 | IB (NA) 66250-D | Addition of Models                                                                                                                                                                   |

|            |                 | Q02CPU-A, Q02HCPU-A, Q06HCPU-A, A2USHCPU-S1, A2USH board                                                                                                                             |

|            |                 | Addition                                                                                                                                                                             |

|            |                 | Section 9.5, APP 2.3                                                                                                                                                                 |

|            |                 | Correction                                                                                                                                                                           |

|            |                 | Section 5.3.2, 6.7.3, 7.8, APP 2.1                                                                                                                                                   |

| Dec., 2000 | IB (NA) 66250-E | Addition                                                                                                                                                                             |

|            |                 | Section 3.9 Correction                                                                                                                                                               |

|            |                 | Section 2.2.3, 3.8.4, 5.3.3, 6.7.1                                                                                                                                                   |

| Dec., 2002 | IB (NA) 66250-F | Addition                                                                                                                                                                             |

| 200., 2002 | .2 () 66266 .   | Section 9.3                                                                                                                                                                          |

|            |                 | Correction                                                                                                                                                                           |

|            |                 | Section 9.2, 9.4, 9.5, 9.6, APP 1.1, APP 1.3                                                                                                                                         |

| Jun., 2003 | IB (NA) 66250-G | Correction                                                                                                                                                                           |

|            |                 | Section 5.5.1, 9.2, 9.3, APP 1.3                                                                                                                                                     |

| Dec., 2003 | IB (NA) 66250-H | Correction                                                                                                                                                                           |

|            |                 | Section 9.4                                                                                                                                                                          |

Japanese Manual Version SH(NA)3436-Q

This manual confers no industrial property rights or any rights of any other kind, nor does it confer any patent licenses. Mitsubishi Electric Corporation cannot be held responsible for any problems involving industrial property rights which may occur as a result of using the contents noted in this manual.

© 1990 Mitsubishi Electric Corporation

\*The manual number is given on the bottom left of the back cover.

| Print Date | *Manual Number  | Revision                                                                                                                                                                                             |

|------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Dec., 2009 | IB (NA) 66250-I | Correction                                                                                                                                                                                           |

|            |                 | Section 3.5, 3.8.1, 5.3.1, 6.4.3, 7.1.1, 7.1.2, 7.1.3, 7.1.4, 7.3.1, 7.4.1, 7.4.6, 7.6.1, 7.6.2, 7.6.3, 7.6.4, 7.6.5, 7.6.6, 7.8.2, 9.1, 9.2, 9.3, 9.4, 9.5, 9.6, APP 1.1, APP 1.2, APP 1.3, APP 1.4 |

|            |                 | Addition                                                                                                                                                                                             |

|            |                 | CONDITIONS OF USE FOR THE PRODUCT                                                                                                                                                                    |

| Mar., 2011 | IB (NA) 66250-J | Correction                                                                                                                                                                                           |

|            |                 | Section 7.6.1, 7.6.2, 9.4, 9.5, 9.6, APP 1.1, APP 1.3                                                                                                                                                |

|            |                 |                                                                                                                                                                                                      |

|            |                 |                                                                                                                                                                                                      |

|            |                 |                                                                                                                                                                                                      |

|            |                 |                                                                                                                                                                                                      |

|            |                 |                                                                                                                                                                                                      |

|            |                 |                                                                                                                                                                                                      |

|            |                 |                                                                                                                                                                                                      |

|            |                 |                                                                                                                                                                                                      |

|            |                 |                                                                                                                                                                                                      |

|            |                 |                                                                                                                                                                                                      |

|            |                 |                                                                                                                                                                                                      |

|            |                 |                                                                                                                                                                                                      |

|            |                 |                                                                                                                                                                                                      |

|            |                 |                                                                                                                                                                                                      |

|            |                 |                                                                                                                                                                                                      |

|            |                 |                                                                                                                                                                                                      |

|            |                 |                                                                                                                                                                                                      |

|            |                 |                                                                                                                                                                                                      |

|            |                 |                                                                                                                                                                                                      |

|            |                 |                                                                                                                                                                                                      |

|            |                 |                                                                                                                                                                                                      |

|            |                 |                                                                                                                                                                                                      |

|            |                 |                                                                                                                                                                                                      |

|            |                 |                                                                                                                                                                                                      |

|            |                 |                                                                                                                                                                                                      |

|            |                 |                                                                                                                                                                                                      |

|            |                 |                                                                                                                                                                                                      |

## **INTRODUCTION**

Thank you for choosing the Mitsubishi MELSEC-A Series of General Purpose Programmable Controllers. Please read this manual carefully so that the equipment is used to its optimum. A copy of this manual should be forwarded to the end User.

## **CONTENTS**

| 1. | INTE       | 1 – 1 ~ 1 – 3 |                                                                |                |

|----|------------|---------------|----------------------------------------------------------------|----------------|

| 2. | INS        | TRUCTIO       | ONS                                                            | 2 – 1 ~ 2 – 24 |

|    | 2.1        | Classi        | fication                                                       | 2 – 1          |

|    | 2.2        | 2 – 2         |                                                                |                |

|    |            | 2.2.1         | Explanation for instructions lists                             | 2 – 2          |

|    |            | 2.2.2         | Sequence instructions                                          | 2 – 5          |

|    |            | 2.2.3         | Basic instructions                                             | 2 – 8          |

|    |            | 2.2.4         | Application instructions                                       | 2 – 16         |

| 3. | INS        | TRUCTIO       | ON STRUCTURE                                                   | 3 – 1 ~ 3 – 25 |

|    | 3.1        | Instruc       | ction Structure                                                | 3 – 1          |

|    | 3.2        | Bit Pro       | ocessing                                                       | 3 – 3          |

|    |            | 3.2.1         | 1-bit processing                                               | 3 – 3          |

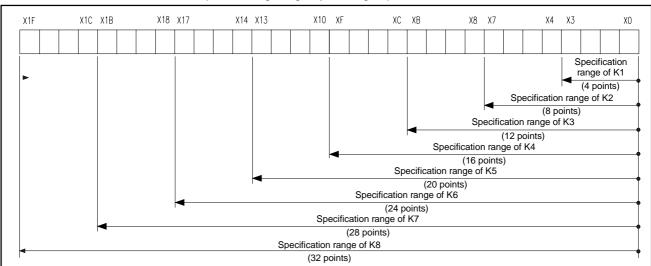

|    |            | 3.2.2         | Digit specification processing                                 | 3 – 3          |

|    | 3.3        | Handli        | ing of Numeric Values                                          | 3 – 6          |

|    | 3.4        | Storing       | g 32-bit Data                                                  | 3 – 8          |

|    | 3.5        | Index         | Qualification                                                  | 3 – 10         |

|    | 3.6        | Subse         | et Processing                                                  | 3 – 12         |

|    | 3.7        |               | tion Error                                                     |                |

|    | 3.8        | •             | ons on Using AnA, A2AS, AnU, QCPU-A (A Mode) and A2USH board   |                |

|    |            | 3.8.1         | The number of steps used in instructions                       | 3 – 14         |

|    |            | 3.8.2         | Instructions of variable functions                             | 3 – 16         |

|    |            | 3.8.3         | Set values for the extension timer and counter                 | 3 – 17         |

|    |            | 3.8.4         | Cautions on using index qualification                          | 3 – 17         |

|    |            | 3.8.5         | Storing 32-bit data in index registers                         | 3 – 20         |

|    | 3.9        | Operation     | on when the OUT Instruction, SET/RST Instruction and           |                |

|    |            | PLS/PL        | F Instruction are from the Same Device                         | 3 – 21         |

| 4. | INS        | TRUCTIO       | ON FORMAT                                                      | 4 – 1 ~ 4 – 4  |

| 5. | SEC        | UENCE         | INSTRUCTIONS                                                   | 5 – 4 ~ 5 – 43 |

|    | 5.1        | Conta         | ct Instructions                                                | 5 – 2          |

|    |            | 5.1.1         | Operation start, series connection, parallel connection        |                |

|    | <b>5</b> 0 | 0             | (LD, LDI, AND, ANI, OR, ORI)                                   |                |

|    | 5.2        |               | ection Instructions                                            |                |

|    |            | 5.2.1         | Ladder block series connection, parallel connection (ANB, ORB) |                |

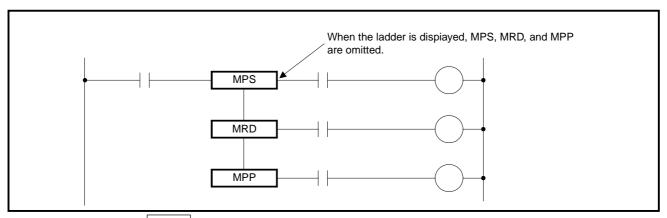

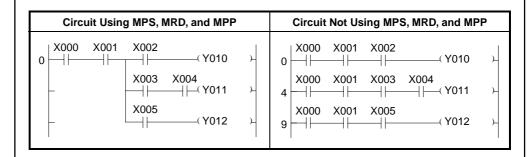

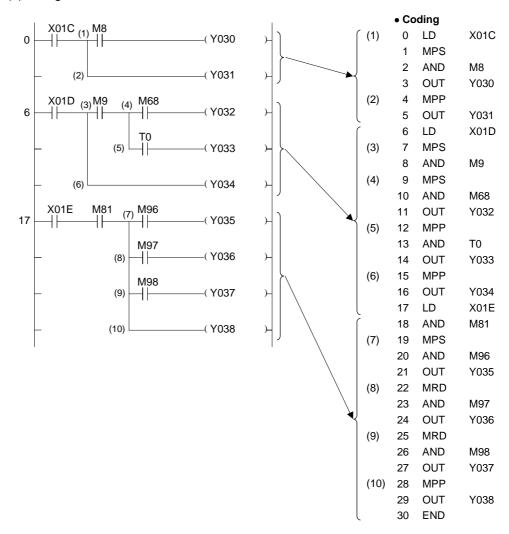

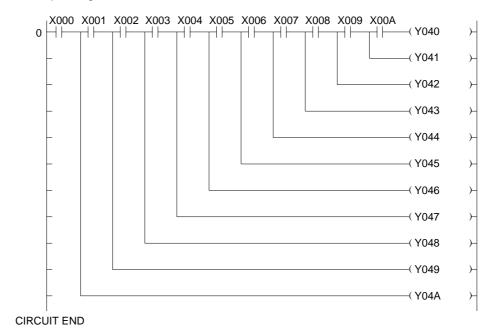

|    |            | 5.2.2         | Operation result push, read, pop (MPS, MRD, MPP)               | 5 – 9          |

|    | 5.3 | Output   | Instructions                                                               | 5 – 14         |

|----|-----|----------|----------------------------------------------------------------------------|----------------|

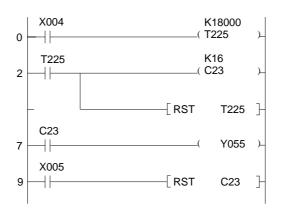

|    |     | 5.3.1    | Bit device, timer, counter output (OUT)                                    | 5 – 14         |

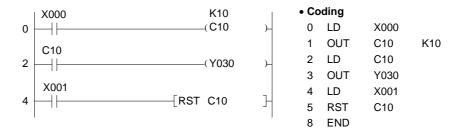

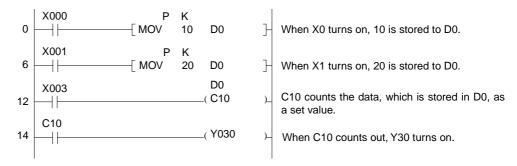

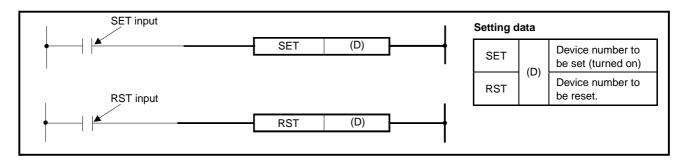

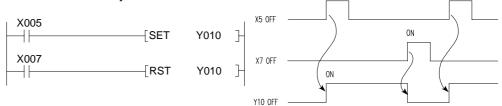

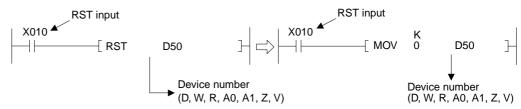

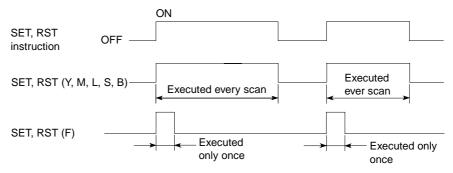

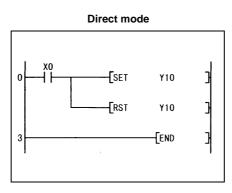

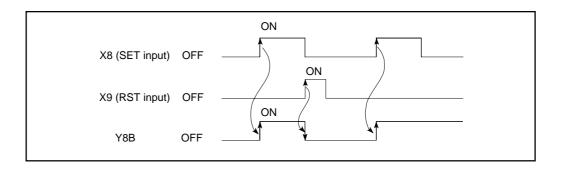

|    |     | 5.3.2    | Bit device set, reset (SET,RST)                                            | 5 – 19         |

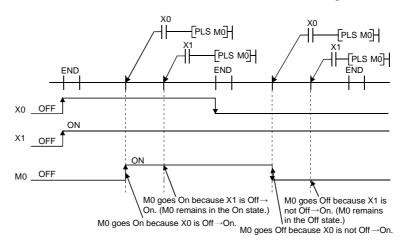

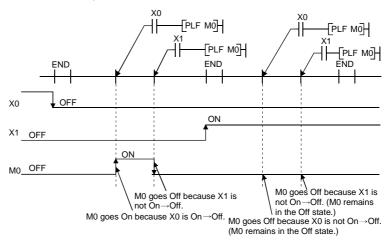

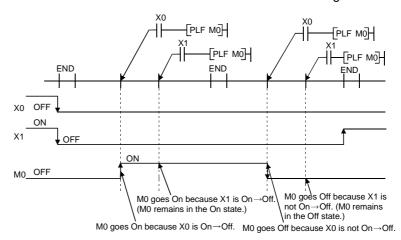

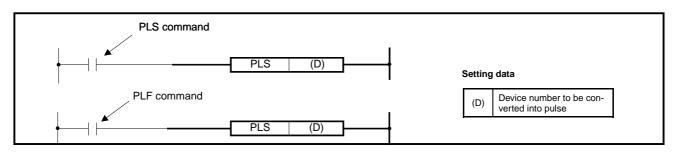

|    |     | 5.3.3    | Edge-triggered differential output (PLS, PLF)                              | 5 – 23         |

|    |     | 5.3.4    | Bit device output reverse (CHK)                                            | 5 – 26         |

|    | 5.4 | Shift In | structions                                                                 | 5 – 28         |

|    |     | 5.4.1    | Bit device shift (SFT, SFTP)                                               | 5 – 28         |

|    | 5.5 | Master   | Control Instructions                                                       | 5 – 30         |

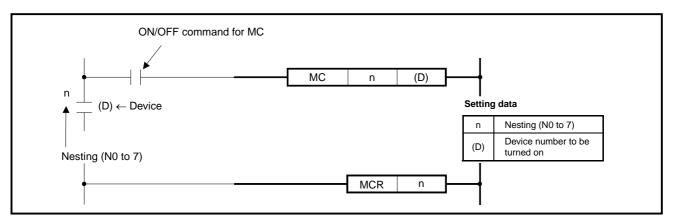

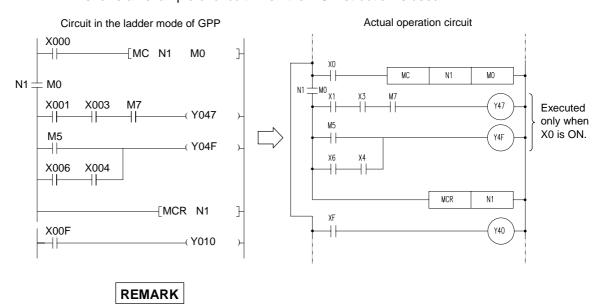

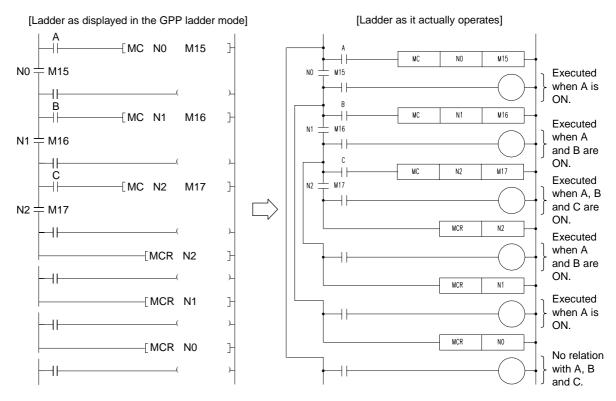

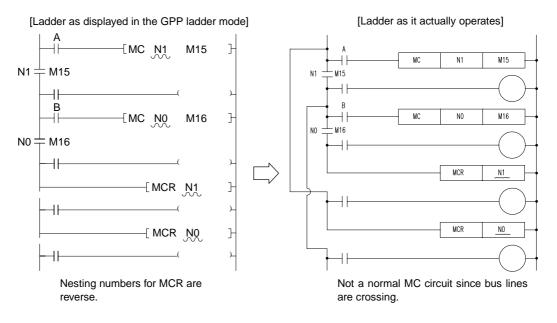

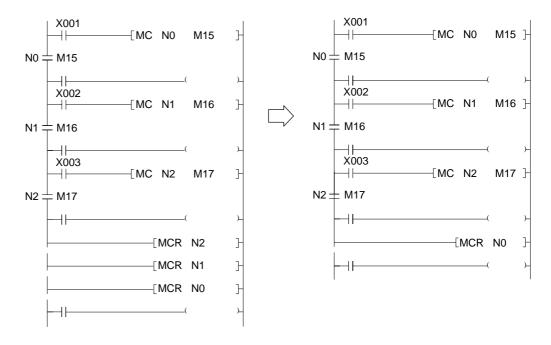

|    |     | 5.5.1    | Master control set, reset (MC, MCR)                                        | 5 – 30         |

|    | 5.6 | Termin   | ation Instructions                                                         | 5 – 34         |

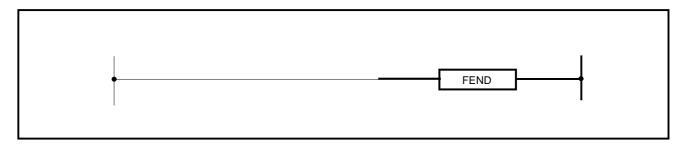

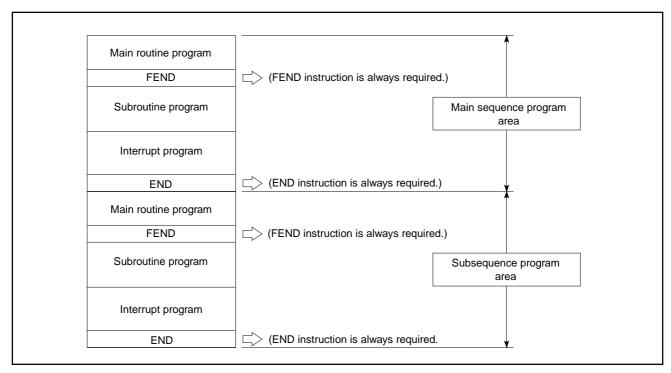

|    |     | 5.6.1    | Main routine program termination (FEND)                                    | 5 – 34         |

|    |     | 5.6.2    | Sequence program termination (END)                                         | 5 – 36         |

|    | 5.7 | Other I  | nstructions                                                                | 5 – 38         |

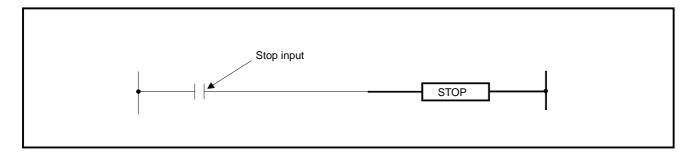

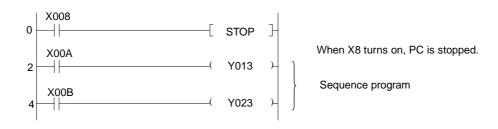

|    |     | 5.7.1    | Sequence program stop (STOP)                                               | 5 – 38         |

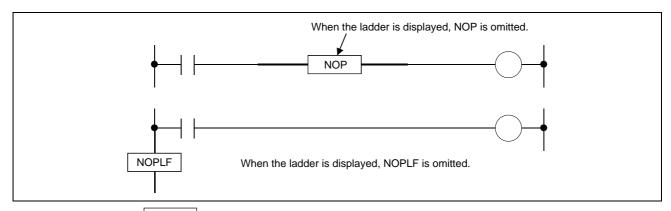

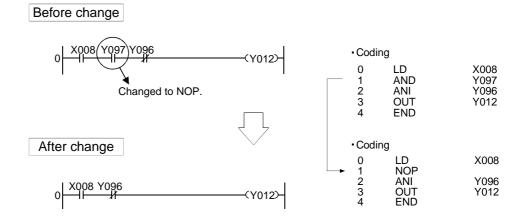

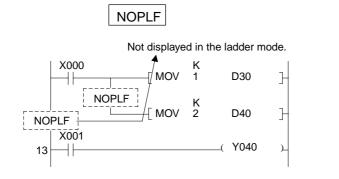

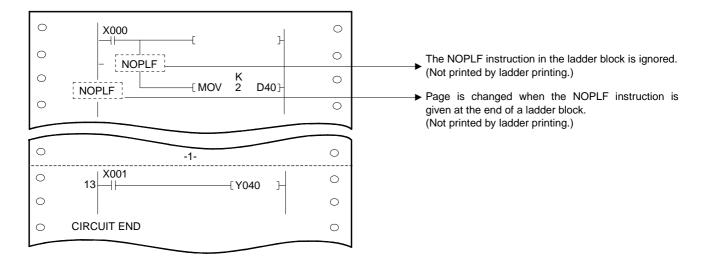

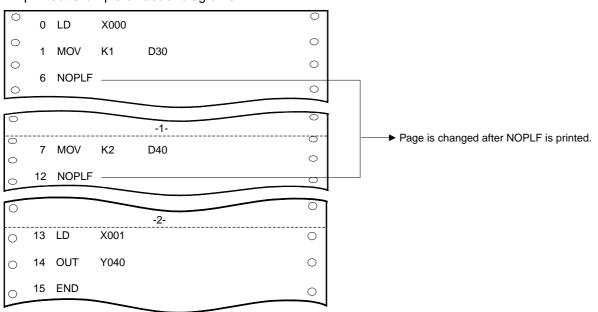

|    |     | 5.7.2    | No operation (NOP, NOPLF)                                                  | 5 – 40         |

| 6. | BAS | IC INSTI | RUCTIONS                                                                   | 6 – 1 ~ 6 – 90 |

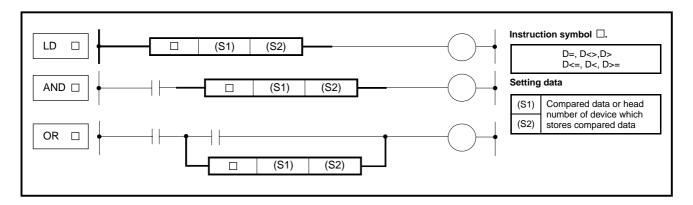

|    | 6.1 | Compa    | arison Operation Instructions                                              | 6 – 2          |

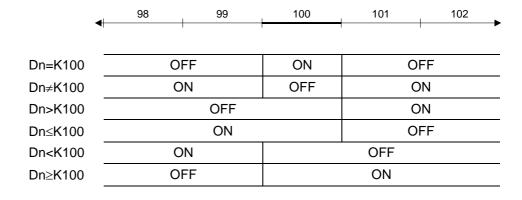

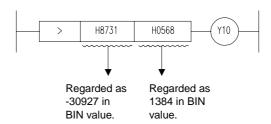

|    |     | 6.1.1    | 16-bit data comparison (=, <>, >, <=, <, >=)                               | 6 – 4          |

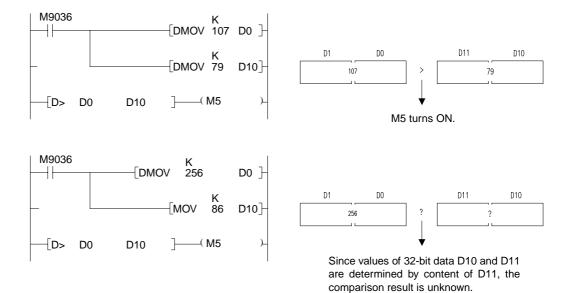

|    |     | 6.1.2    | 32-bit data comparison (D=, D<>, D>, D<=, D<,D>=)                          | 6 – 6          |

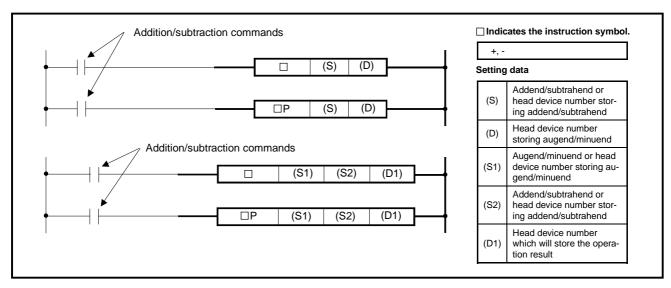

|    | 6.2 | Arithme  | etic Operation Instructions                                                | 6 – 8          |

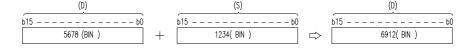

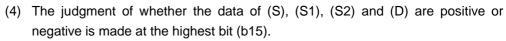

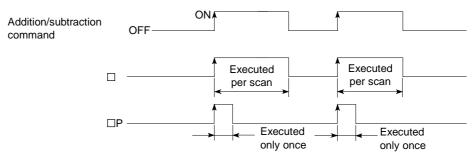

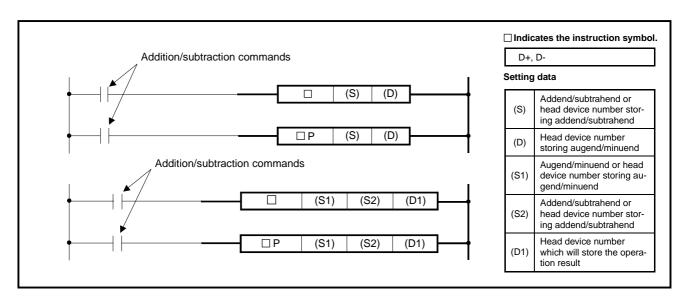

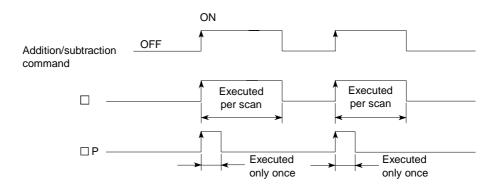

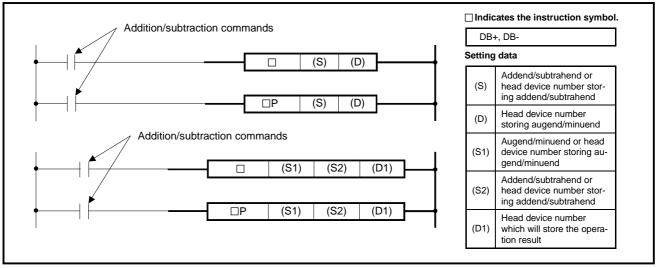

|    |     | 6.2.1    | BIN 16-bit addition, subtraction (+, +P, -, -P)                            | 6 – 10         |

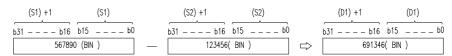

|    |     | 6.2.2    | BIN 32-bit addition, subtraction (D+, D+P, D-, D-P)                        | 6 – 13         |

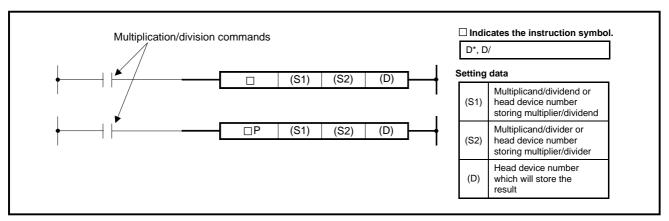

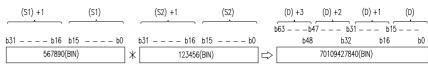

|    |     | 6.2.3    | BIN 16-bit multiplication, division (*, *P, /, /P)                         | 6 – 16         |

|    |     | 6.2.4    | BIN 32-bit multiplication, division (D*, D*P, D/, D/P)                     | 6 – 19         |

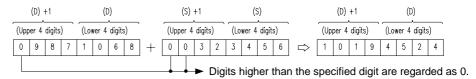

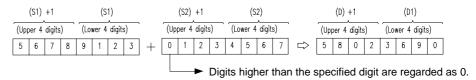

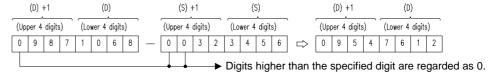

|    |     | 6.2.5    | BCD 4-digit addition, subtraction (B+, B+P, B-, B-P)                       | 6 – 22         |

|    |     | 6.2.6    | BCD 8-digit addition, subtraction (DB+, DB+P, DB-, DB-P)                   | 6 – 25         |

|    |     | 6.2.7    | BCD 4-digit multiplication, division (B*, B*P, B/, B/P)                    | 6 – 28         |

|    |     | 6.2.8    | BCD 8-digit multiplication, division (DB*, DB*P, DB/, DB/P)                | 6 – 31         |

|    |     | 6.2.9    | 16-bit BIN data increment, decrement (INC, INCP, DEC, DECP)                | 6 – 34         |

|    |     | 6.2.10   | 32-bit BIN data increment, decrement (DINC, DINCP, DDEC, DDECP)            | 6 – 36         |

|    | 6.3 | BCD ←    | BIN Conversion Instructions                                                | 6 – 38         |

|    |     | 6.3.1    | BIN data $\rightarrow$ BCD 4-, 8-digit conversion (BCD, BCDP, DBCD, DBCDP) | 6 – 39         |

|    |     | 6.3.2    | BCD 4-, 8-digit $\rightarrow$ BIN data conversion (BIN, BINP, DBIN, DBINP) | 6 – 42         |

|    | 6.4 | Data Tr  | ransfer Instructions                                                       | 6 – 46         |

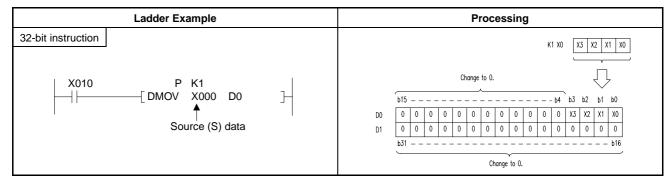

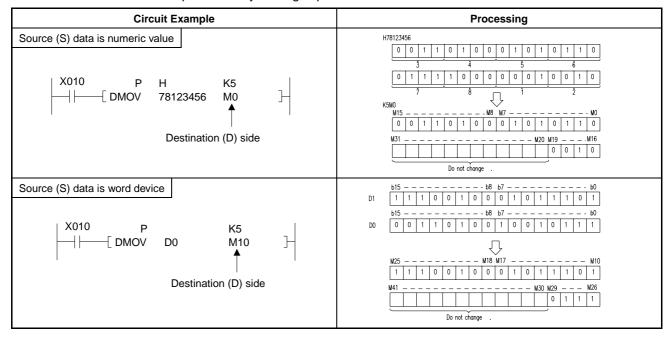

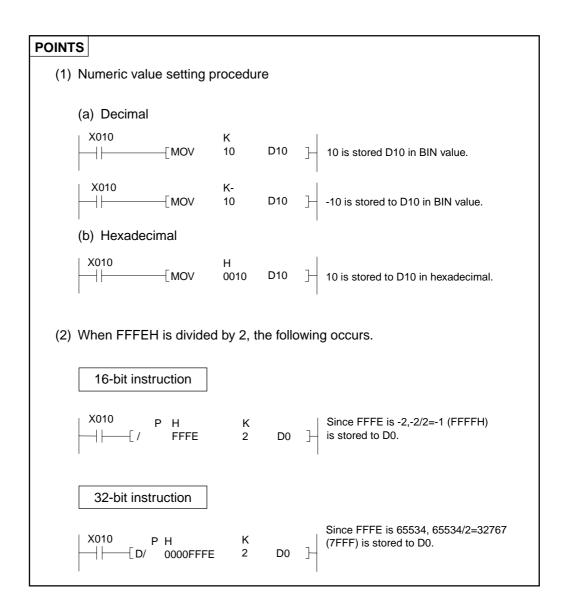

|    |     | 6.4.1    | 16-, 32-bit data transfer (MOV, MOVP, DMOV, DMOVP)                         | 6 – 47         |

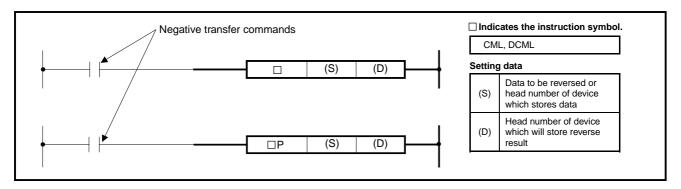

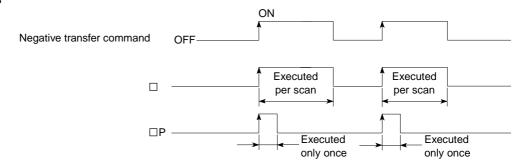

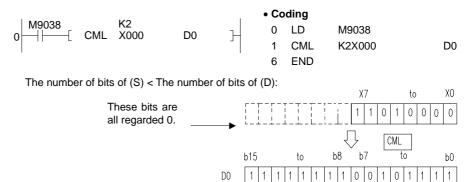

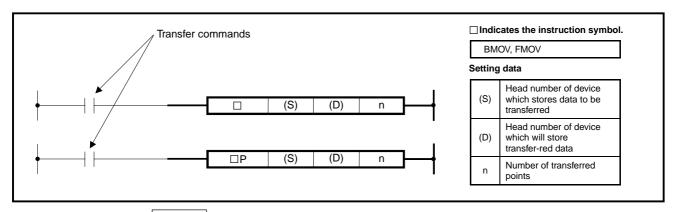

|    |     | 6.4.2    | 16-, 32-bit data negation transfer (CML, CMLP, DCML, DCMLP)                | 6 – 49         |

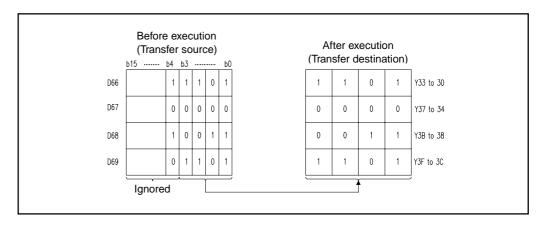

|    |     | 6.4.3    | 16-bit data block transfer (BMOV, BMOVP, FMOV, FMOVP)                      | 6 – 52         |

|    |     | 6.4.4    | 16 32-bit data exchange (XCH, XCHP, DXCH, DXCHP)                           | 6 – 56         |

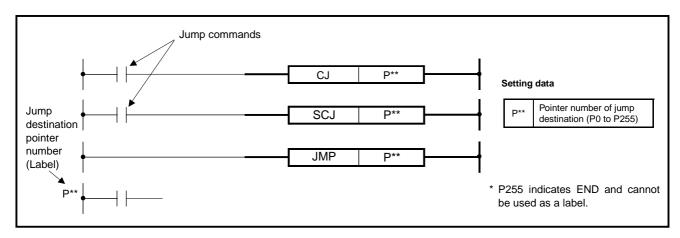

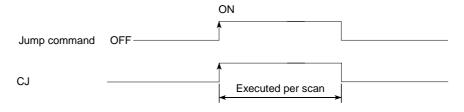

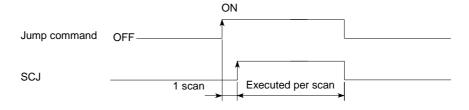

|    | 6.5 | Progra   | m Branch Instructions                                                 | 6 –   | - 58 |

|----|-----|----------|-----------------------------------------------------------------------|-------|------|

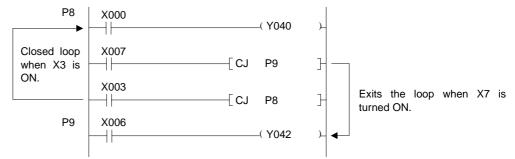

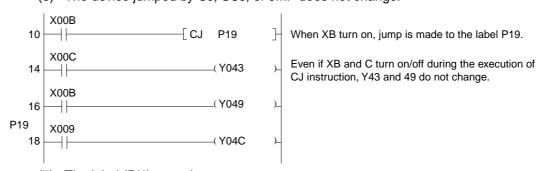

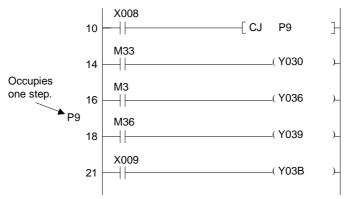

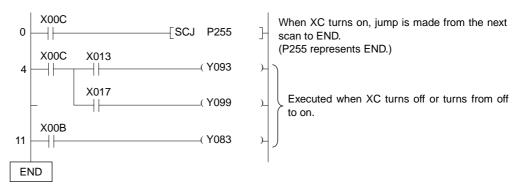

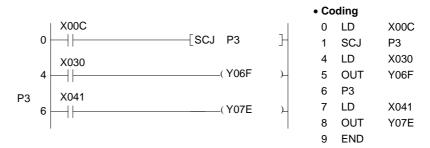

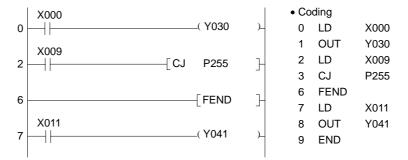

|    |     | 6.5.1    | Conditional jump, unconditional jump (CJ, SCJ, JMP)                   | 6 –   | - 58 |

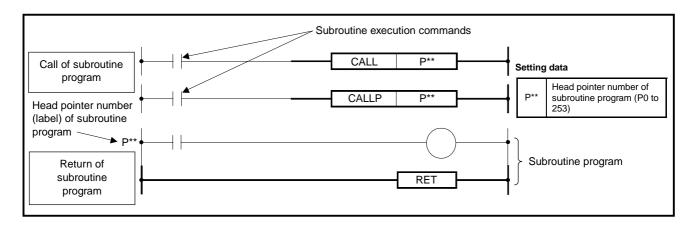

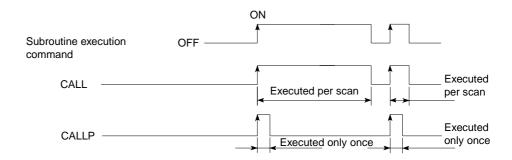

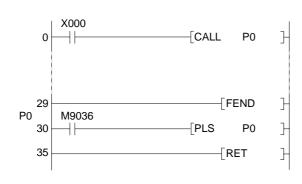

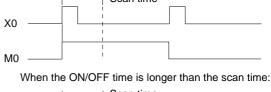

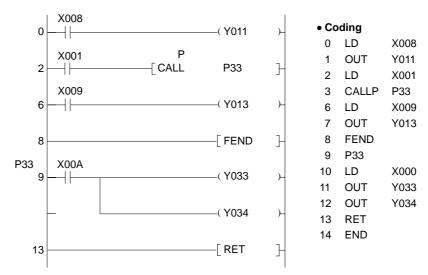

|    |     | 6.5.2    | Subroutine call, return (CALL, CALLP, RET)                            | 6 –   | - 62 |

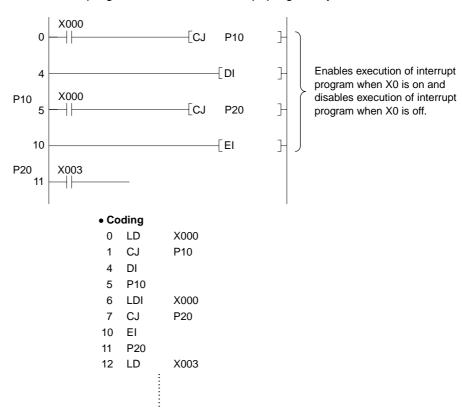

|    |     | 6.5.3    | Interrupt enable, disable, return (EI, DI, IRET)                      | 6 –   | - 65 |

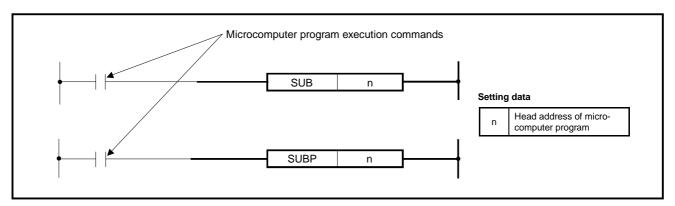

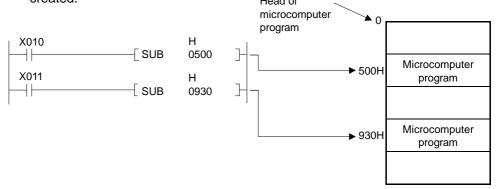

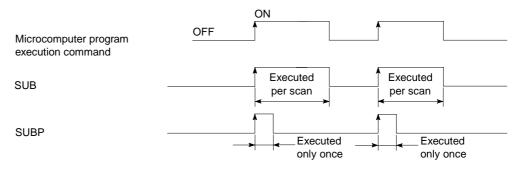

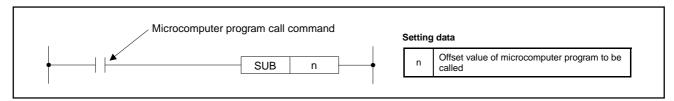

|    |     | 6.5.4    | Microcomputer program call (SUB, SUBP)                                | 6 –   | - 68 |

|    | 6.6 | Progra   | m Switching Instructions                                              | 6 -   | - 70 |

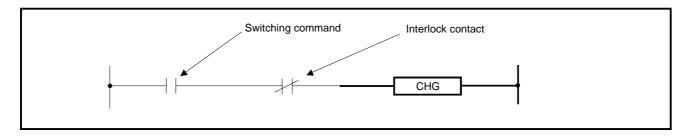

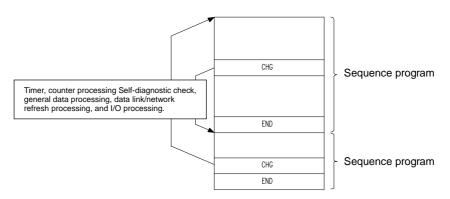

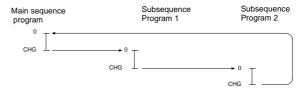

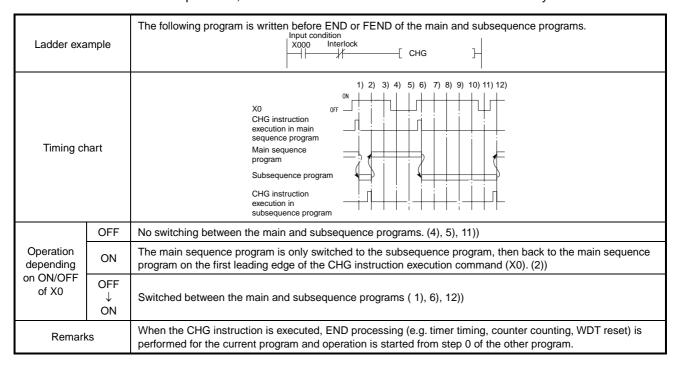

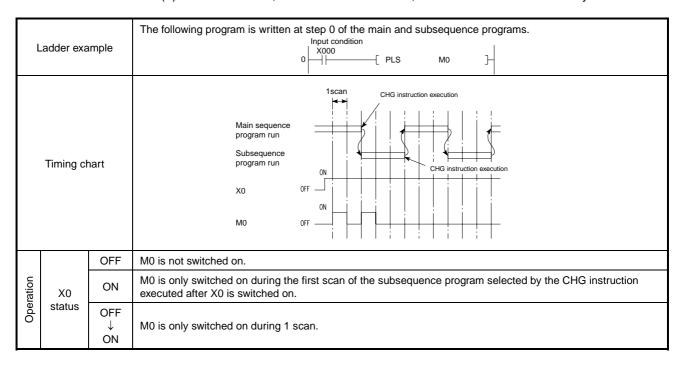

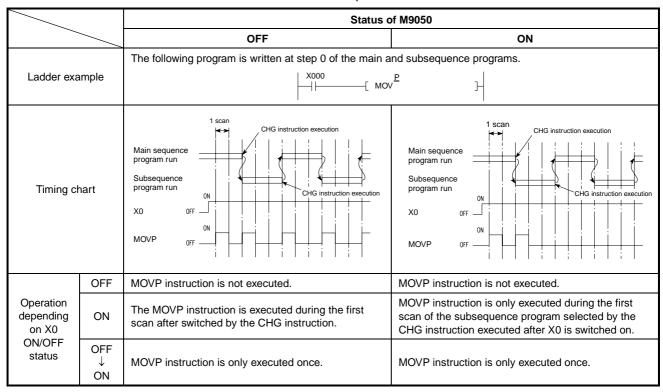

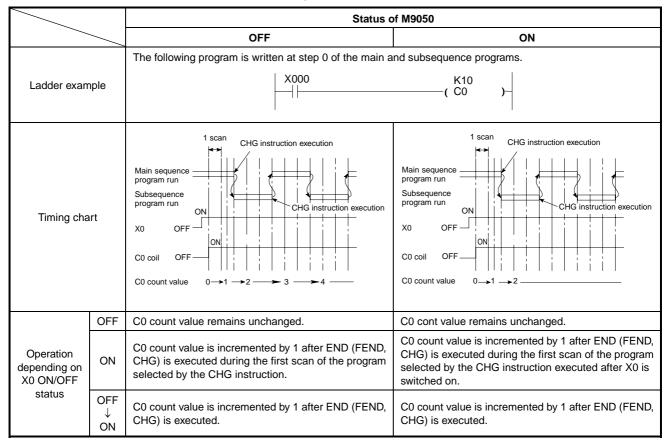

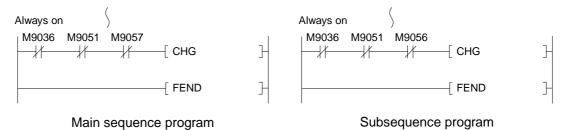

|    |     | 6.6.1    | Main ↔ subprogram switching (CHG)                                     | 6 –   | - 70 |

|    | 6.7 | Link R   | efresh Instructions                                                   | 6 –   | - 83 |

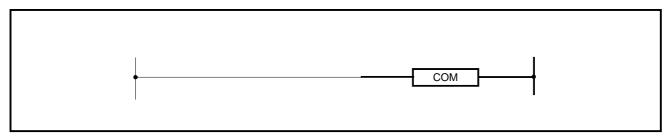

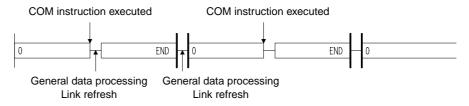

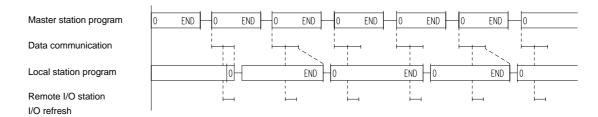

|    |     | 6.7.1    | Link refresh (COM)                                                    | 6 -   | - 83 |

|    |     | 6.7.2    | Link refresh enable, disable (EI, DI)                                 | 6 -   | - 85 |

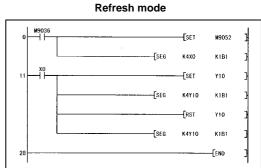

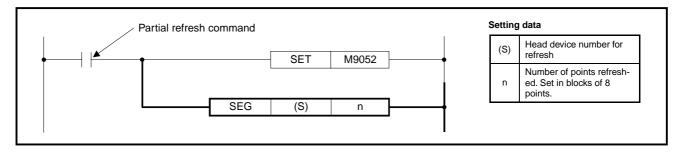

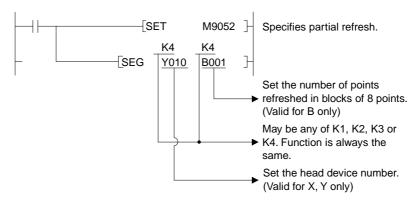

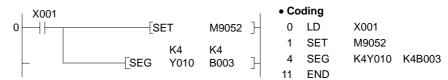

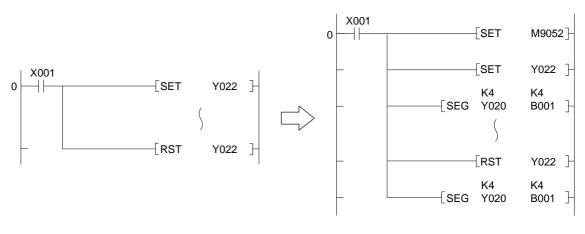

|    |     | 6.7.3    | Partial refresh (SEG)                                                 | 6 -   | - 88 |

| 7. | APP | LICATIO  | ON INSTRUCTIONS7 – 1                                                  | ~ 7 - | 148  |

|    | 7.1 | Logica   | Il Operation Instructions                                             | 7     | - 2  |

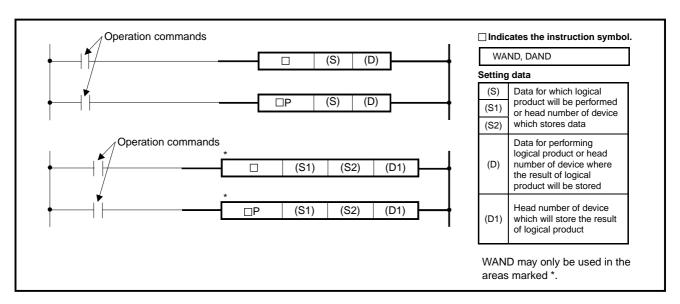

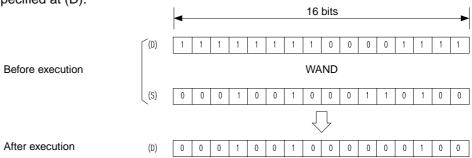

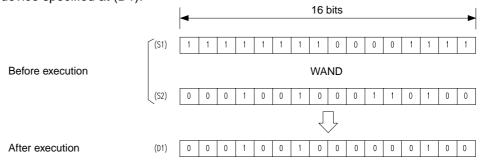

|    |     | 7.1.1    | 16-, 32-bit data logical product (WAND, WANDP, DAND, DANDP)           | 7     | – 3  |

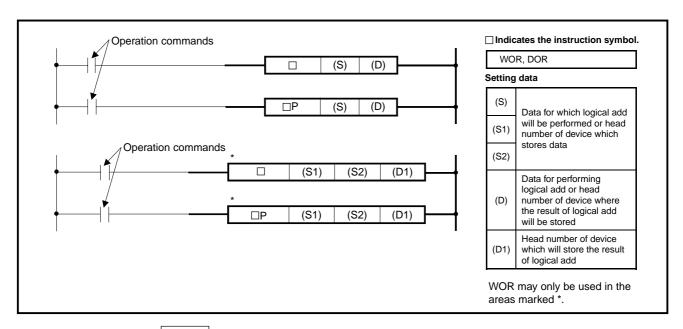

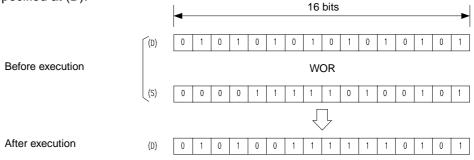

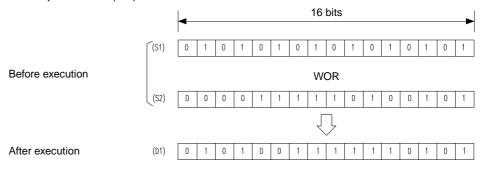

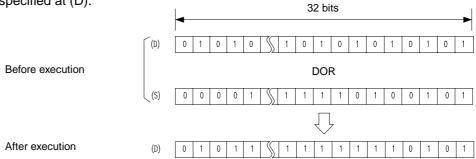

|    |     | 7.1.2    | 16-, 32-bit data logical add (WOR, WORP, DOR, DORP)                   | 7     | - 8  |

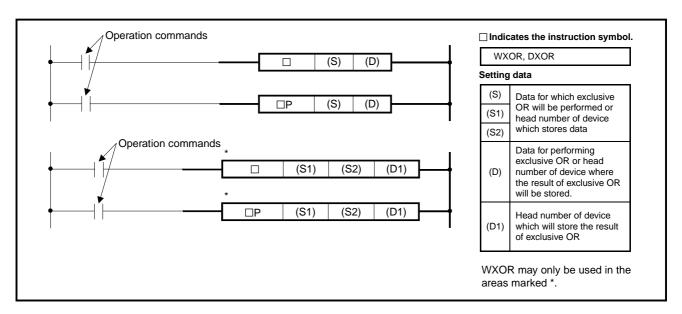

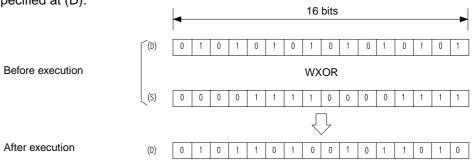

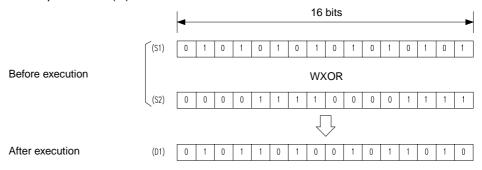

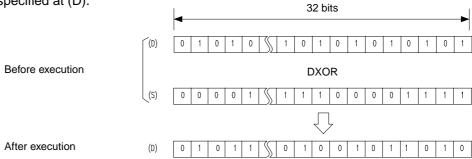

|    |     | 7.1.3    | 16-, 32-bit data exclusive logical add (WXOR, WXORP, DXOR, DXORP)     | 7 –   | - 12 |

|    |     | 7.1.4    | 16, 32-bit data NOT exclusive logical add (WXNR, WXNRP, DXNR, DXNRP)  | 7 –   | - 16 |

|    |     | 7.1.5    | BIN 16-bit data 2's complement (NEG, NEGP)                            |       |      |

|    | 7.2 | Rotatio  | on Instructions                                                       | 7 –   | - 22 |

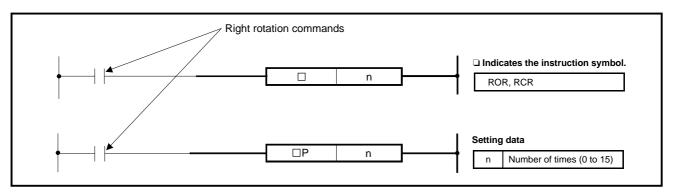

|    |     | 7.2.1    | 16-bit data right rotation (ROR, RORP, RCR, PCRP)                     |       |      |

|    |     | 7.2.2    | 16-bit data left rotation (ROL, ROLR, RCL, RCLP)                      | 7 –   | - 25 |

|    |     | 7.2.3    | 32-bit data right rotation (DROR, DRORP, DRCR, DRCRP)                 | 7 –   | - 27 |

|    |     | 7.2.4    | 32-bit data left rotation (DROL, DROLP, DRCL, DRCLP)                  | 7 –   | - 29 |

|    | 7.3 | Shift Ir | nstructions                                                           | 7 –   | - 31 |

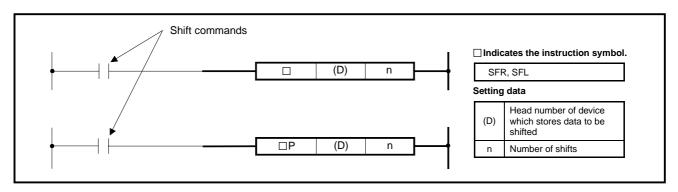

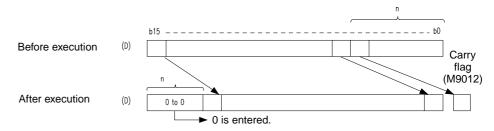

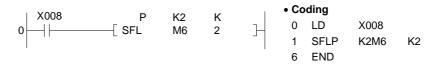

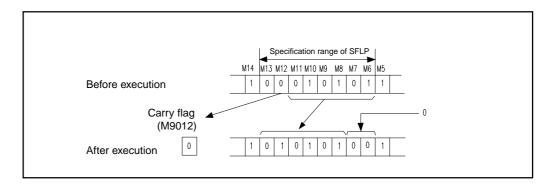

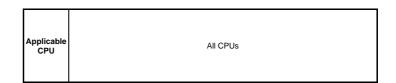

|    |     | 7.3.1    | 16-bit data n-bit right shift, left shift (SFR, SFRP, SFL, SFLP)      | 7 –   | - 32 |

|    |     | 7.3.2    | n-bit data 1-bit right shift, left shift (BSFR, BSFRP, BSFL, BSFLP)   | 7 –   | - 35 |

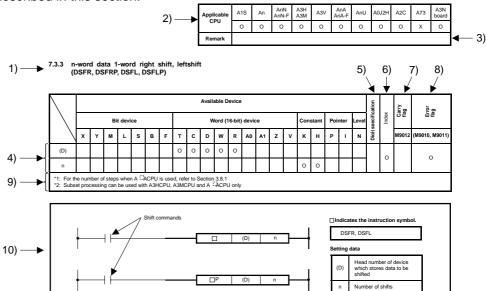

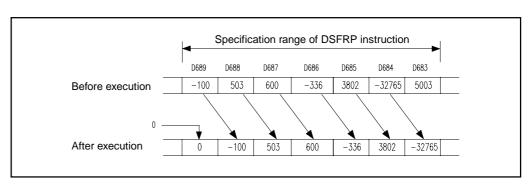

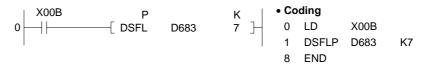

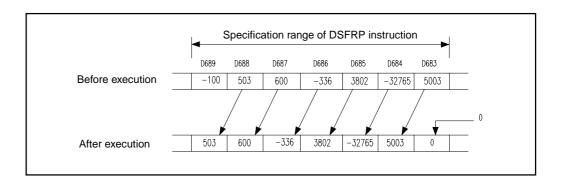

|    |     | 7.3.3    | n-word data 1-word right shift, left shift (DSFR, DSFRP, DSFL, DSFLP) | 7 –   | - 37 |

|    | 7.4 | Data F   | Processing Instructions                                               | 7 –   | - 40 |

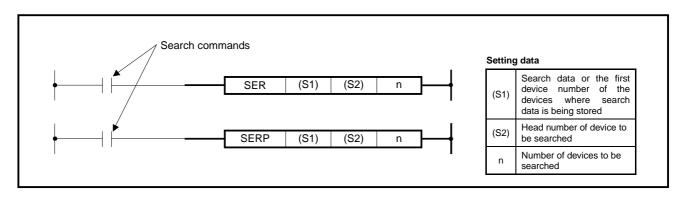

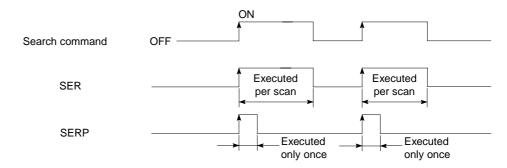

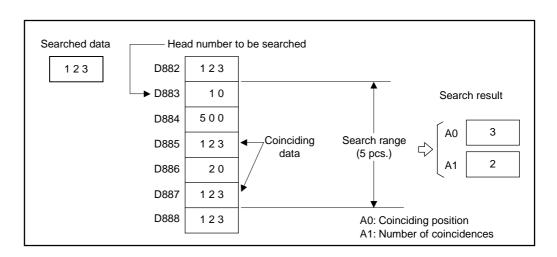

|    |     | 7.4.1    | 16-bit data search (SER, SERP)                                        | 7 –   | - 41 |

|    |     | 7.4.2    | 16-, 32-bit data bit check (SUM, SUMP, DSUM, DSUMP)                   | 7 –   | - 43 |

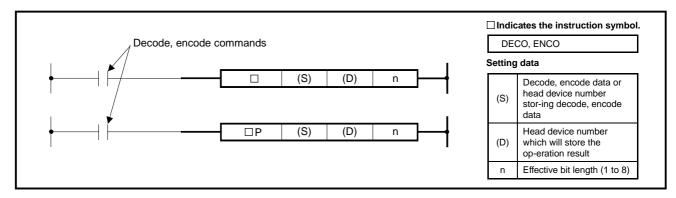

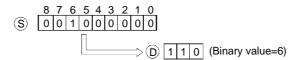

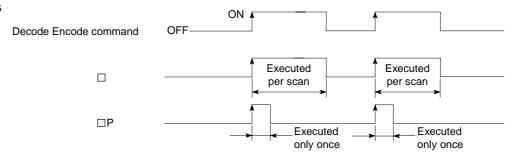

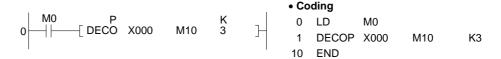

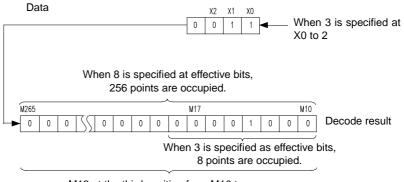

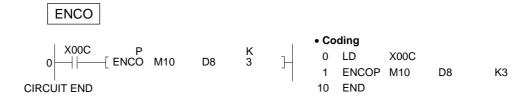

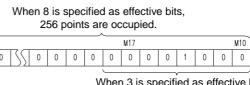

|    |     | 7.4.3    | $8\leftrightarrow$ 256-bit decode, encode (DECO, DECOP, ENCO, ENCOP)  | 7 –   | - 46 |

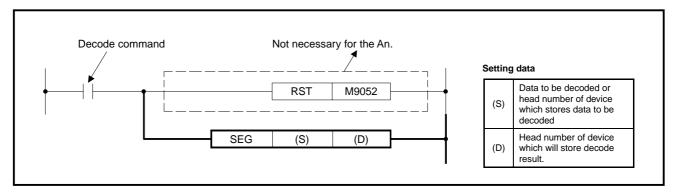

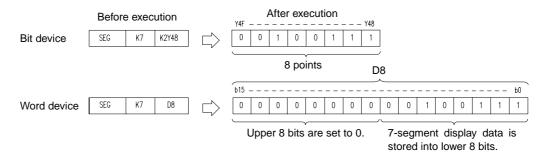

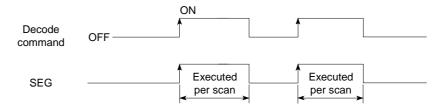

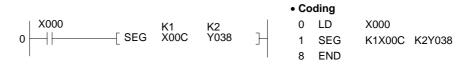

|    |     | 7.4.4    | 7 segment decode (SEG)                                                | 7 –   | - 49 |

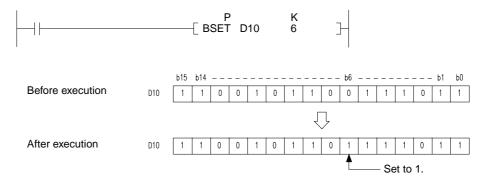

|    |     | 7.4.5    | Word device bit set, reset (BSET, BSETP, BRST, BRSTP)                 | 7 –   | - 52 |

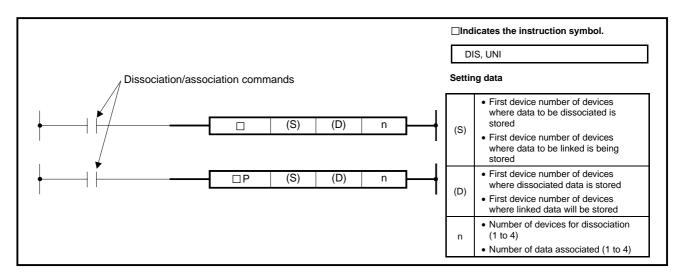

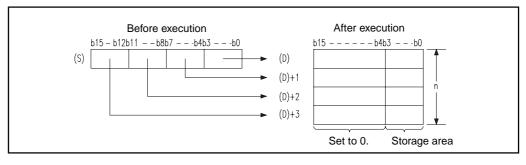

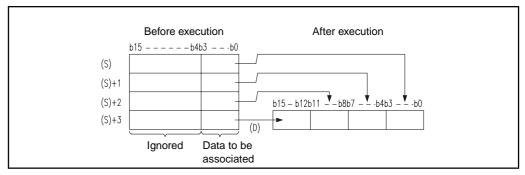

|    |     | 7.4.6    | 16-bit data dissociation, association (DIS, DISP, UNI, UNIP)          | 7 –   | - 54 |

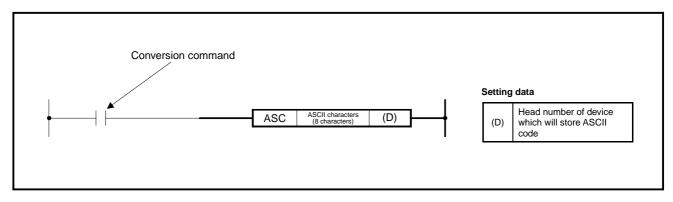

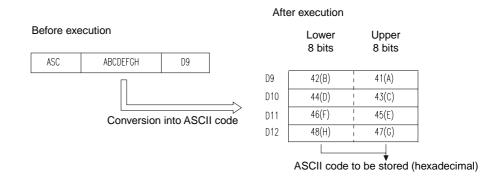

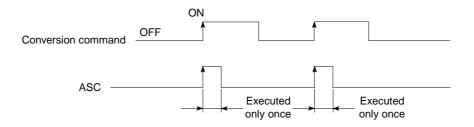

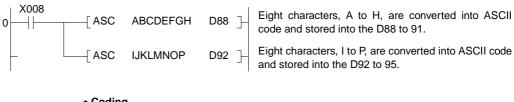

|    |     | 7.4.7    | ASCII code conversion (ASC)                                           | 7 –   | - 57 |

|    | 7.5 | FIFO I   | nstructions                                                           | 7 –   | - 59 |

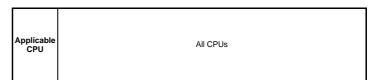

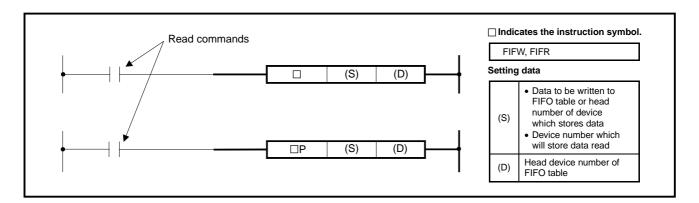

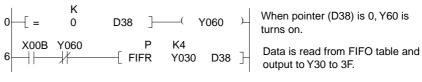

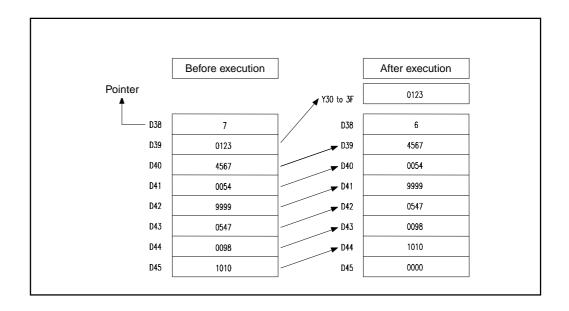

|    |     | 7.5.1    | FIFO table write, read (FIFW, FIFWP, FIFR, FIFRP)                     | 7 –   | - 60 |

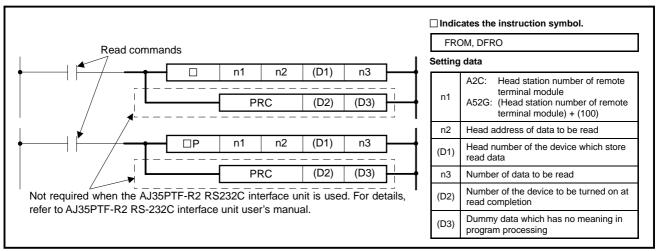

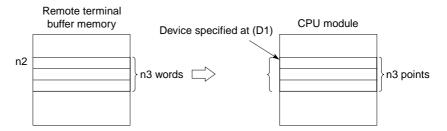

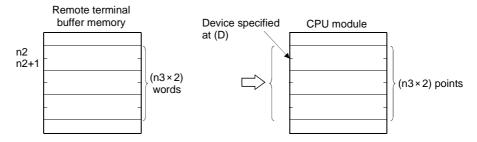

|    | 7.6 | Buffer   | Memory Access Instructions                                            | 7 -   | - 64 |

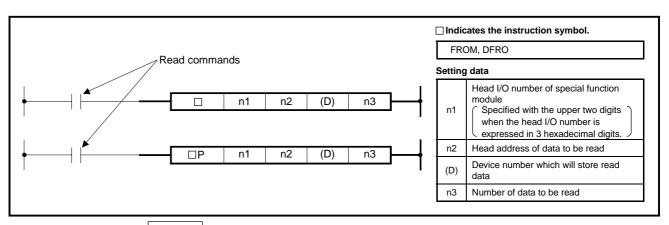

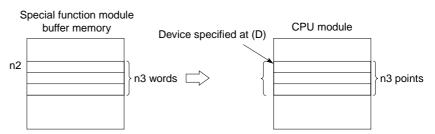

|      | 7.6.1   | Special function module 1-, 2-word data read (FROM, FROMP, DFRO, DFRO   | ЭР)7 – 65      |

|------|---------|-------------------------------------------------------------------------|----------------|

|      | 7.6.2   | Special function module 1-, 2-word data write (TO, TOP, DTO, DTOP)      | 7 – 68         |

|      | 7.6.3   | Remote terminal module 1- and 2-word data read                          |                |

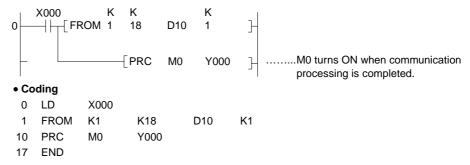

|      |         | (FROM, PRC, FROMP, PRC, DFRO, PRC, DFROP, PRC)                          | 7 – 71         |

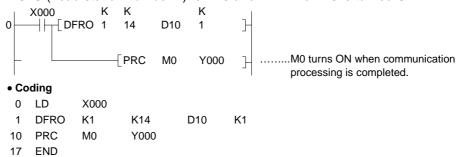

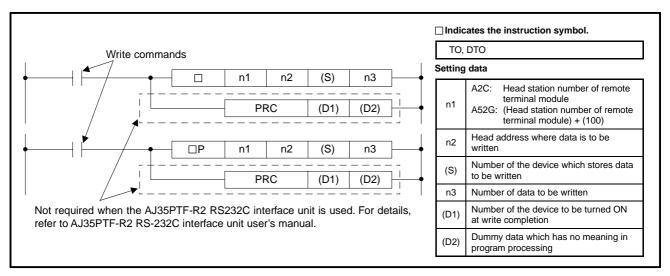

|      | 7.6.4   | Remote terminal module 1- and 2-word data write                         |                |

|      |         | (TO, PRC, TOP, PRC, DTO, PRC, DTOP, PRC)                                | 7 – 76         |

|      | 7.6.5   | Special module/special block 1-, 2-word data read                       | 7 00           |

|      | 7.0.0   | (FROM, FROMP, DFRO, DFROP)                                              |                |

| 77   | 7.6.6   | Special module/special block 1-, 2-word data write (TO, TOP, DTO, DTOP) |                |

| 7.7  |         | NEXT Instructions                                                       |                |

|      | 7.7.1   | FOR to NEXT (FOR, NEXT)                                                 |                |

| 7.8  |         | Remote I/O Station Access Instructions                                  |                |

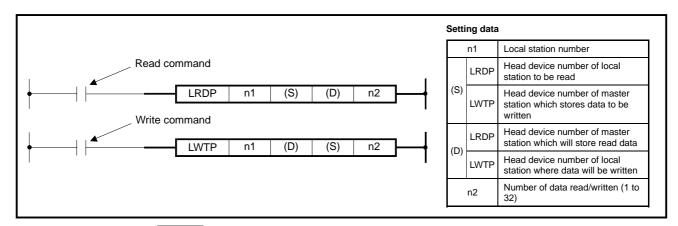

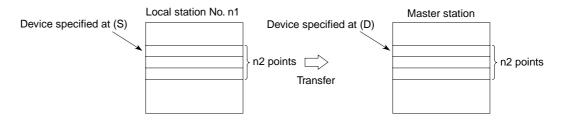

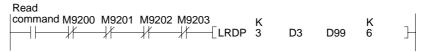

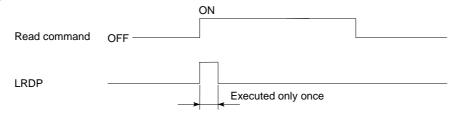

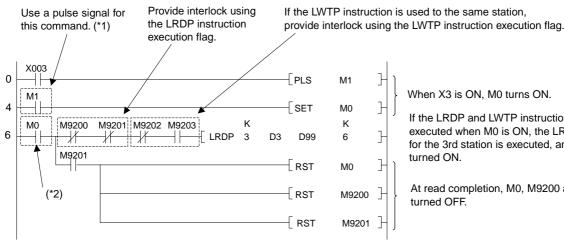

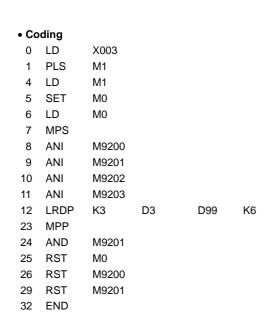

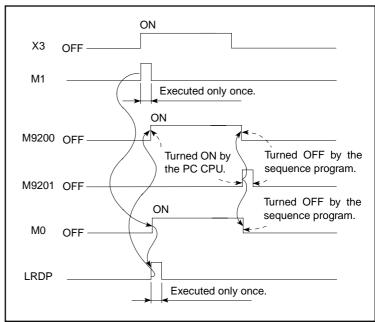

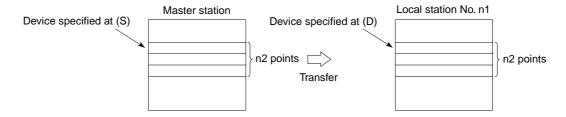

|      | 7.8.1   | Local station data read, write (LRDP, LWTP)                             |                |

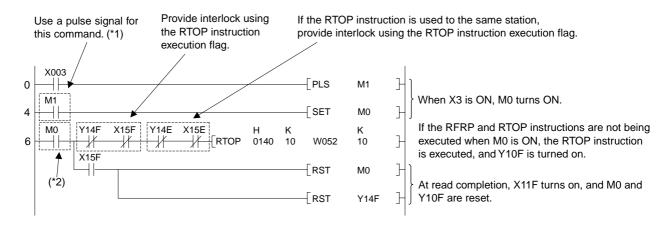

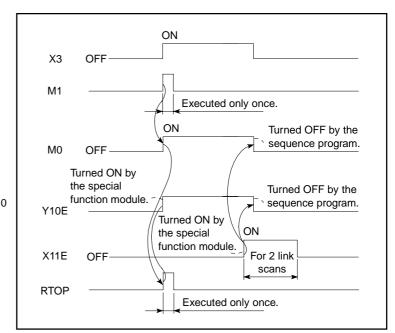

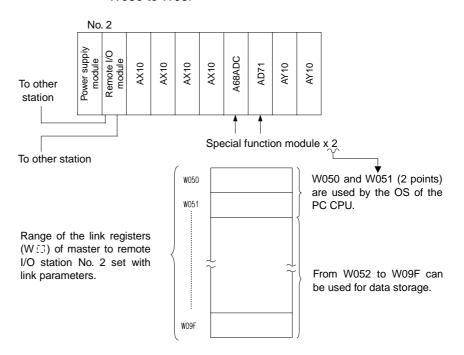

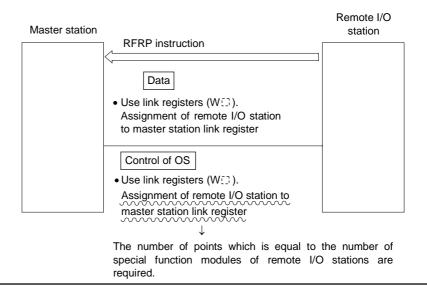

|      | 7.8.2   | Remote I/O station data read, write (RFRP, RTOP)                        |                |

| 7.9  |         | / Instructions                                                          |                |

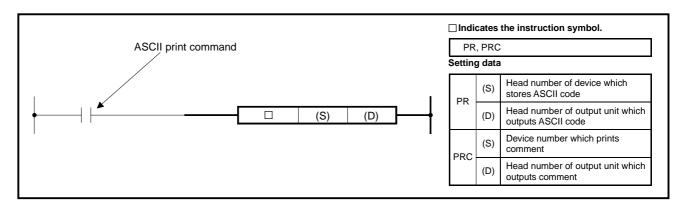

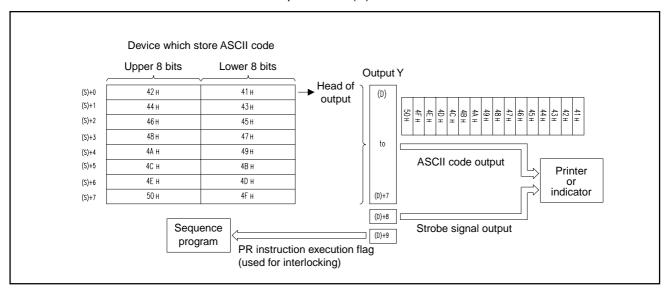

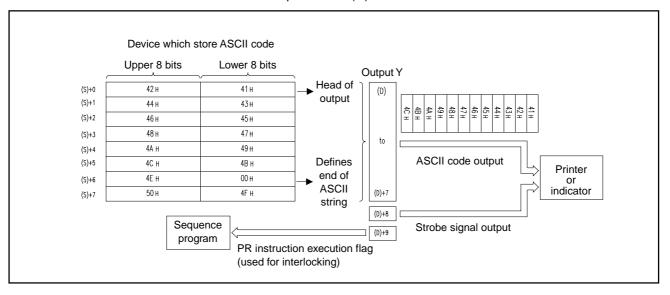

|      | 7.9.1   | ASCII code print instructions (PR, PRC)                                 |                |

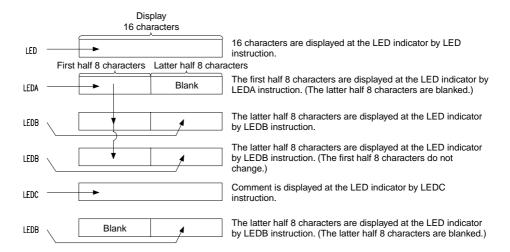

|      | 7.9.2   | ASCII code comment display instructions (LED, LEDC)                     | 7 – 113        |

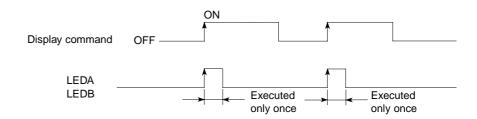

|      | 7.9.3   | Character display instructions (LEDA, LEDB)                             | 7 – 116        |

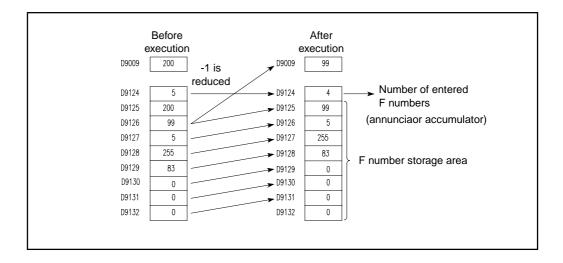

|      | 7.9.4   | Annunciator reset instruction (LEDR)                                    | 7 – 118        |

| 7.10 | Other I | nstructions                                                             | 7 – 121        |

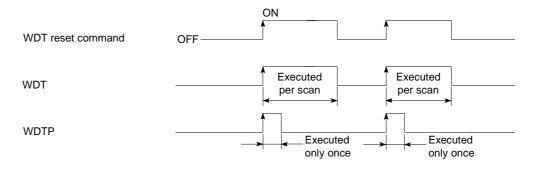

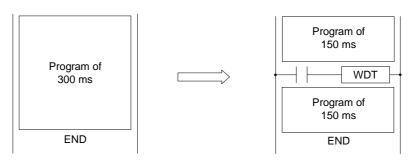

|      | 7.10.1  | WDT reset (WDT, WDTP)                                                   | 7 – 122        |

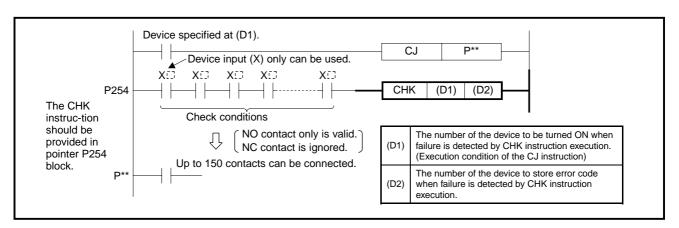

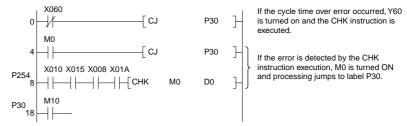

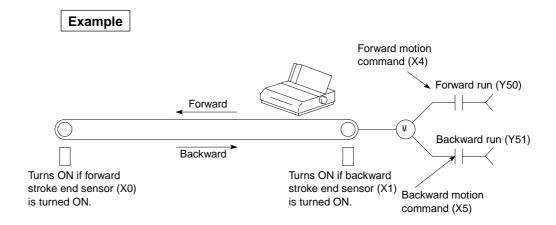

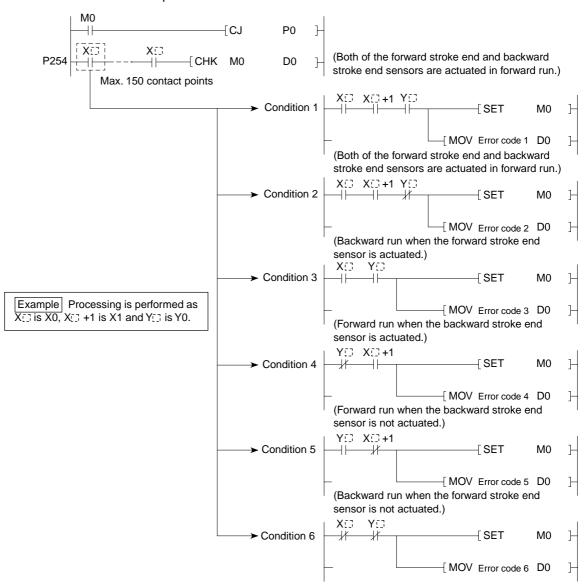

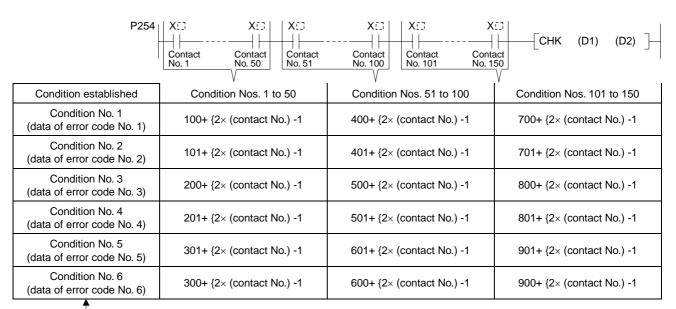

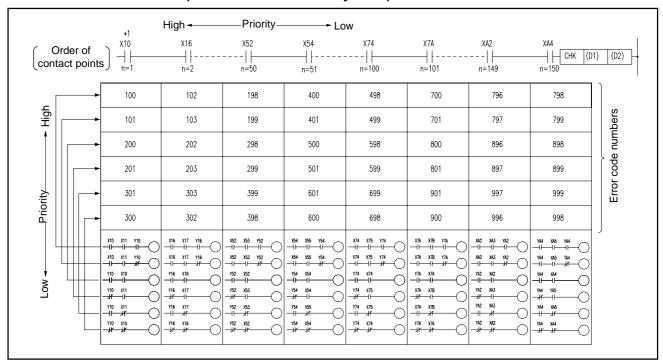

|      | 7.10.2  | Specific format failure check (CHK)                                     | 7 – 124        |

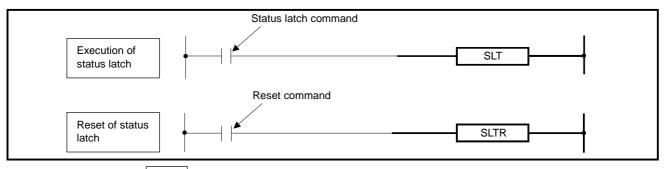

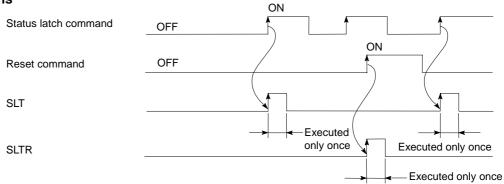

|      | 7.10.3  | Status latch set, reset (SLT, SLTR)                                     | 7 – 131        |

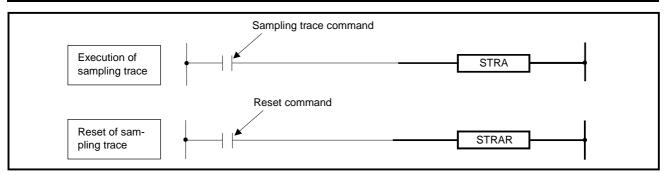

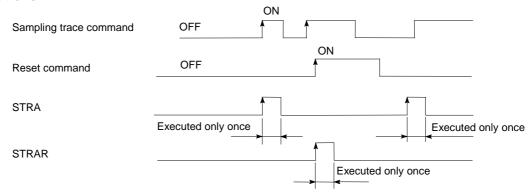

|      | 7.10.4  | Sampling trace set, reset (STRA, STRAR)                                 | 7 – 133        |

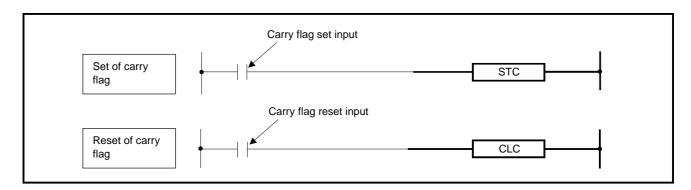

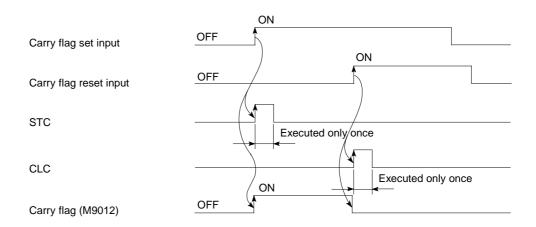

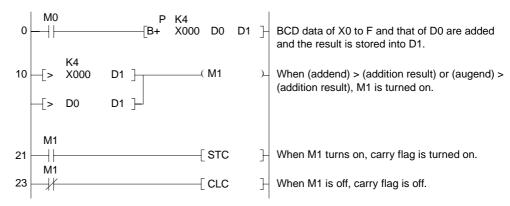

|      | 7.10.5  | Carry flag set, reset (STC, CLC)                                        | 7 – 135        |

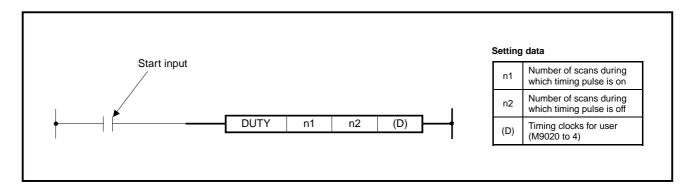

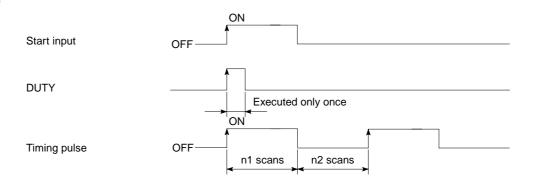

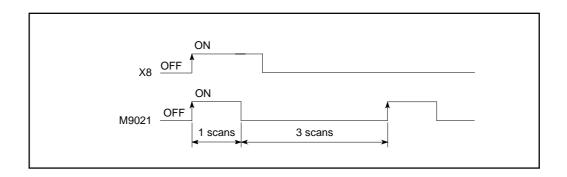

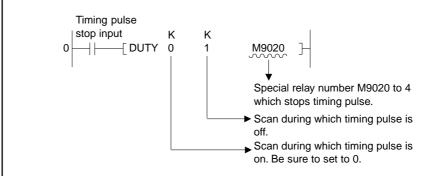

|      | 7.10.6  | Pulse regeneration instruction (DUTY)                                   | 7 – 137        |

| 7.11 | Servo I | Program Instructions                                                    | 7 – 139        |

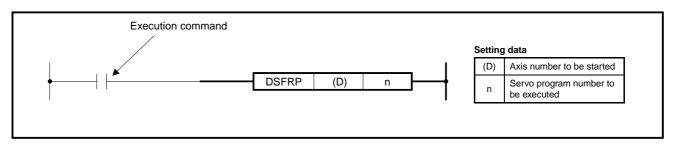

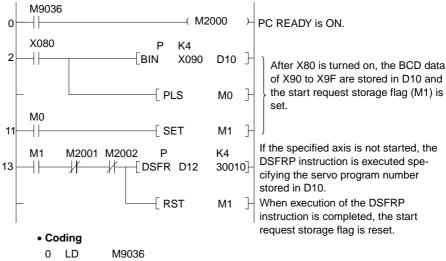

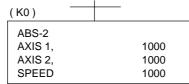

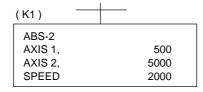

|      | 7.11.1  | Servo program start (DSFRP)                                             | 7 – 140        |

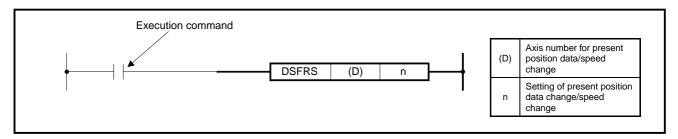

|      | 7.11.2  | Present position data and speed change instruction (DSFLP)              | 7 – 144        |

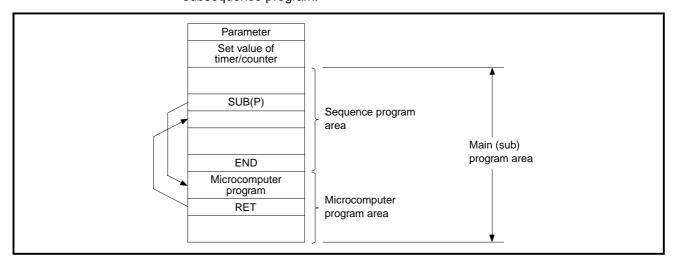

| MICR | сосомі  | PUTER MODE                                                              | 8 – 1 ~ 8 – 16 |

| 8.1  | Specifi | cations of Microcomputer Mode                                           | 8 – 1          |

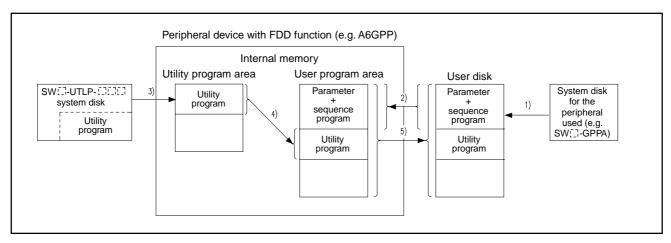

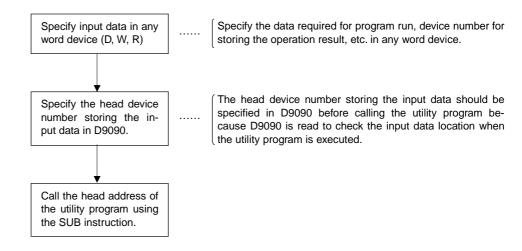

| 8.2  | -       | Jtility Program                                                         |                |

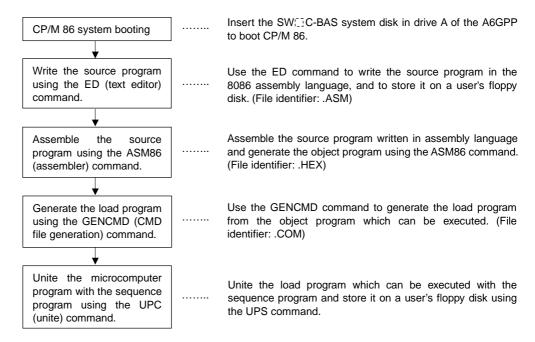

| 8.3  | •       | Jser-Written Microcomputer Programs                                     |                |

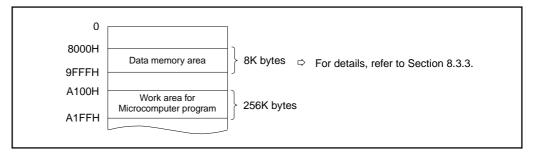

| 0.0  | 8.3.1   | Memory map                                                              |                |

|      | 8.3.2   | Data memory area address configuration                                  |                |

|      | 8.3.3   | Differences in operations called by microcomputer instructions          | – 0            |

|      | 0.0.0   | according to CPU models                                                 | 8 – 7          |

|      | 8.3.4   | Configuration of data memory area                                       |                |

|      |         |                                                                         |                |

8.

| 9. | ERR  | OR CODE LIST   |                                                               | 9 – 1 ~ 9 – 39     |

|----|------|----------------|---------------------------------------------------------------|--------------------|

|    | 9.1  | Reading Error  | Codes                                                         | 9 – 1              |

|    | 9.2  | Error Code Lis | t for the An, AnN, A3H, A3M, A3V, A0J2H, AnS, A2C, A73, A52G, | A1FX and A3N       |

|    |      | board          |                                                               | 9 – 1              |

|    | 9.3  | Error Code Lis | t for the AnSHCPU                                             | 9 – 6              |

|    | 9.4  | Error Code Lis | st for the AnACPU and A3A Board                               | 9 – 11             |

|    | 9.5  | Error Code Lis | st for the AnUCPU, A2ASCPU and A2USH board                    | 9 – 20             |

|    | 9.6  | Error Code Lis | st for the QCPU-A (A Mode)                                    | 9 – 31             |

| ΑP | PEND | ICES           | AI                                                            | PP – 1 ~ APP – 100 |

|    | APP  | ENDIX 1 LISTS  | OF SPECIAL RELAYS AND SPECIAL REGISTERS                       | APP – 1            |

|    |      | Appendix 1.1   | List of Special Relays                                        | APP – 1            |

|    |      | Appendix 1.2   | Special Relays for Link                                       | APP – 13           |

|    |      | Appendix 1.3   | Special Registers                                             | APP – 16           |

|    |      | Appendix 1.4   | Special Registers for Link                                    | APP – 35           |

|    | APP  | ENDIX 2 OPER   | ATION PROCESSING TIME                                         | APP – 40           |

|    |      | Appendix 2.1   | Instruction Processing Time of Small Size, Compact CPUs       | APP – 42           |

|    |      | Appendix 2.2   | Instruction Processing Time of CPUs                           | APP – 68           |

|    |      | Appendix 2.3   | List of Instruction Processing Time of QCPU-A (A Mode)        | APP – 81           |

|    | APP  | ENDIX 3 ASCII  | CODE TABLE                                                    | APP – 92           |

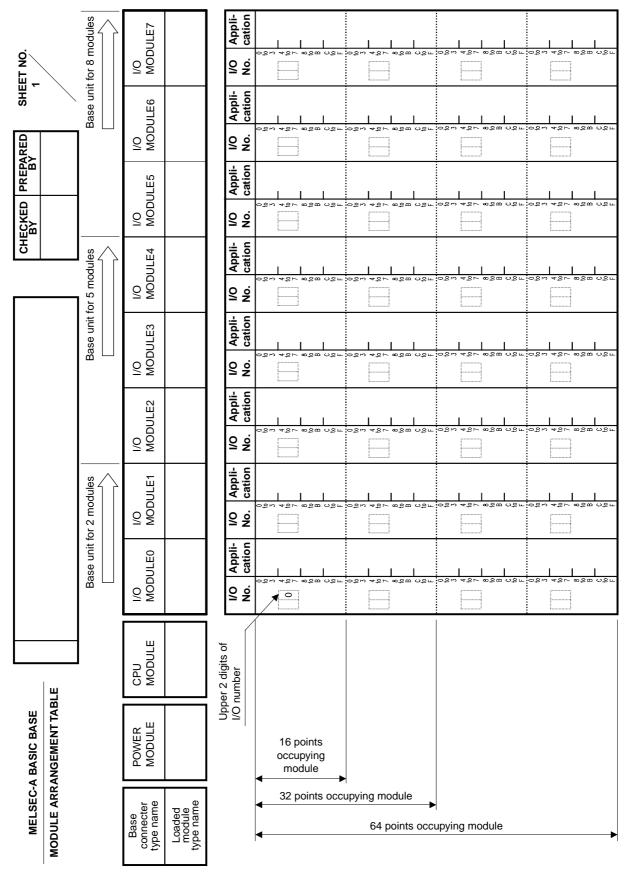

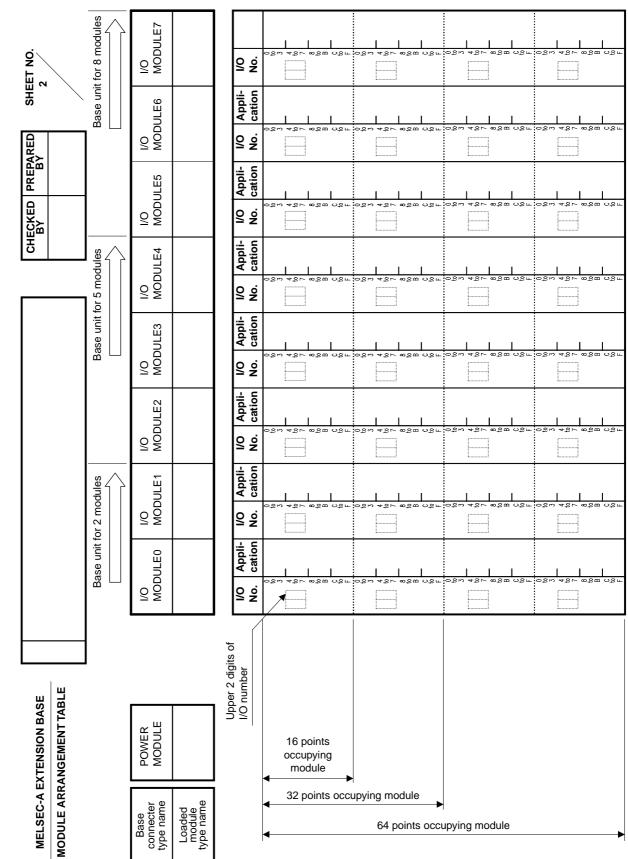

|    | APP  | ENDIX 4 FORM   | MATS OF PROGRAM SHEETS                                        | APP – 93           |

| MEMO |  |  |  |

|------|--|--|--|

|      |  |  |  |

|      |  |  |  |

|      |  |  |  |

|      |  |  |  |

|      |  |  |  |

|      |  |  |  |

|      |  |  |  |

|      |  |  |  |

|      |  |  |  |

|      |  |  |  |

|      |  |  |  |

|      |  |  |  |

|      |  |  |  |

|      |  |  |  |

|      |  |  |  |

|      |  |  |  |

|      |  |  |  |

|      |  |  |  |

|      |  |  |  |

|      |  |  |  |

#### 1. INTRODUCTION

This manual explains how to use the MELSEC-A series sequence control instructions and microcomputer programs.

MELSEC-A series programmable controllers have a parameter which is used to designate functions and device use ranges.

The functions and device use ranges are determined by the parameter values. The parameters of CPU are set to default values. If the default can be used for the purpose, it is not necessary to set the parameter.

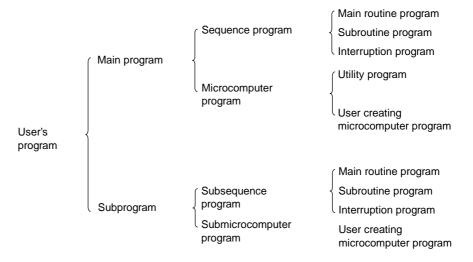

The user's programs for the MELSEC-A series PCs are classified as follows. ACPU Programming Manual (fundamental) gives the programs which can be used for CPUs.

Table 1.1 gives the applicable CPUs the abbreviations used in this manual.

Table 1.1 Applicable CPUs and the Abbreviations Used in This Manual

| Abbreviations use | d in this manual | Applicable CPUs                                         |  |

|-------------------|------------------|---------------------------------------------------------|--|

|                   | A1               | A1CPU(P21/R21)                                          |  |

| An                | A2(-S1)          | A2CPU(P21/R21), A2CPU(P21/R21)-S1                       |  |

|                   | A3               | A3CPU(P21/R21)                                          |  |

|                   | A1N              | A1NCPU(P21/R21)                                         |  |

| AnN               | A2N(-S1)         | A2NCPU(P21/R21), A2NCPU(P21/R21)-S1                     |  |

|                   | A3N              | A3NCPU(P21/R21)                                         |  |

| A3                | Н                | A3HCPU(P21/R21)                                         |  |

| A3I               | M                | A3MCPU(P21/R21)                                         |  |

| A3'               | V                | A3VCPU(P21/R21)                                         |  |

| AnA               | A2A(-S1)         | A2ACPU(P21/R21), A2ACPU(P21/R21)-S1                     |  |

| AllA              | A3A              | A3ACPU(P21/R21)                                         |  |

| AOJ               | 2H               | A0J2HCPU(P21/R21)                                       |  |

| AnS               | A1S              | A1SCPU, A1SCPU-S1, A1SCPUC24-R2, A1SJCPU, A1SJCPU-S3    |  |

| Allo              | A2S              | A2SCPU, A2SCPU-S1                                       |  |

| AnSH              | A1SH             | A1SHCPU, A1SJHCPU, A1SJHCPU-S8                          |  |

| Allon             | A2SH             | A2SHCPU, A2SHCPU-S1                                     |  |

| A2                | C                | A2CCPU(P21/R21), A2CCPUDC24, A2CCPUC24(-PRF), A2CCPU-S3 |  |

| A3N b             | oard             | A7BDE-A3N-PT32-S3                                       |  |

| A2USH             | board            | Type A80BDE-A2USH-S1 PLC CPU Board                      |  |

| A7                | 3                | A73CPU(P21/R21)                                         |  |

| A52               | G                | A52GCPU(T21B)                                           |  |

|                   | A2U(-S1)         | A2UCPU, A2UCPU-S1                                       |  |

| AnU               | A3U              | A3UCPU                                                  |  |

|                   | A4U              | A4UCPU                                                  |  |

| A2AS              | A2AS(-S1)        | A2ASCPU, A2ASCPU-S1, A2ASCPU-S30                        |  |

| AZAS              | A2USH-S1         | A2USHCPU-S1                                             |  |

|                   | Q02              | Q02CPU-A                                                |  |

| QCPU-A (A Mode)   | Q02H             | Q02HCPU-A                                               |  |

|                   | Q06H             | Q06HCPU-A                                               |  |

| A1F               | X                | A1FXCPU                                                 |  |

Table 1.2 Peripheral Devices and the Abbreviations Used in This Manual

| Abbreviations used in this manual | Peripheral devices      |                                                    |  |

|-----------------------------------|-------------------------|----------------------------------------------------|--|

| GPP                               | A6GPP<br>A6HGP<br>A6PHP | IBM PC/AT(GPP function) A7HGP A7PHPE(GPP function) |  |

## **POINT**

This manual cannot be used in reference to the A0J2CPU(P23/R23). For the instructions which can be used for the A0J2CPU(P23/R23), refer to the A0J2CPU Programming Manual. (IB-66057)

## Also refer to the following manuals for writing programs for the A series PCs.

| Topic                                                                                                                                              | Content                                                                                                                                                                                  | Reference Manual                                                               |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--|

| <ul> <li>Memory capacity and the number of devices of the CPU module.</li> <li>Specifications of power supply modules, base units, etc.</li> </ul> |                                                                                                                                                                                          |                                                                                |  |

| CPU functions                                                                                                                                      | <ul> <li>System configuration for PC.</li> <li>Performance and functions of the CPU module.</li> <li>Processings of the CPU module.</li> <li>Lists of devices and parameters.</li> </ul> | User's Manual for respective CPU module                                        |  |

| Writing programs      Programming procedures.     Description of devices and parameters.     Kinds of programs.     Configuration of memory areas. |                                                                                                                                                                                          | ACPU programming Manual (Fundamentals) IB(NA)-66249                            |  |

|                                                                                                                                                    | Description of dedicated instructions<br>(extended application instructions).                                                                                                            | AnSHCPU/AnACPU/AnUCPU Programming Manual (Dedicated Instructions) IB(NA)-66251 |  |

| To use A2A(S1)<br>and A3ACPU                                                                                                                       | Description of the AD57 control instructions.                                                                                                                                            | AnACPU/AnUCPU Programming Manual (AD57 Instructions) IB(NA)-66257              |  |

|                                                                                                                                                    | Description of the PID control instructions.                                                                                                                                             | AnACPU/AnUCPU Programming Manual (PID Instructions.) IB(NA)-66258              |  |

| To Use A73CPU                                                                                                                                      | <ul><li>Positioning control.</li><li>Writing servo programs.</li><li>Description of auxiliary and application functions.</li></ul>                                                       | A73CPU Reference Manual IB(NA)-66233                                           |  |

## 2. INSTRUCTIONS

## 2.1 Classification

The instructions of MELSEC-A series are largely classified into sequence instructions, basic instructions, and application instructions. These instructions are shown in Table 2.1.

**Table 2.1 Classification of Instructions**

| Clas        | sification of instructions                   | Description                                                                                                      | page           |

|-------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------|----------------|

|             | Contact instruction                          | Operation start, series connection, parallel connection                                                          | 5-2 to 5-4     |

|             | Connection instruction                       | Ladder block connection, operation result storage/read                                                           | 5-5 to 5-13    |

| Sequence    | Output instruction                           | Bit device output, pulse output, output reverse                                                                  | 5-14 to 5-26   |

| instruction | Shift instruction                            | Bit device shift                                                                                                 | 5-28 to 5-29   |

|             | Master control instruction                   | Master control                                                                                                   | 5-30 to 5-33   |

|             | Termination instruction                      | Program termination                                                                                              | 5-34 to 5-35   |

|             | Other instructions                           | Program stop, no operation, etc.                                                                                 | 5-36 to 5-43   |

|             | Comparison operation instruction             | Comparison such as =, >, and <                                                                                   | 6-2 to 6-7     |

|             | Arithmetic operation instruction             | Addition, subtraction, multiplication, and division of BIN and BCD                                               | 6-8 to 6-37    |

| Basic       | BCD ↔ BIN conversion instruction             | Conversion from BCD to BIN and BIN to BCD                                                                        | 6-38 to 6-45   |

| instruction | Data transfer instruction                    | Transfer of specified data                                                                                       | 6-46 to 6-57   |

|             | Program branch instruction                   | Program jump, subroutine/interrupt program call                                                                  | 6-58 to 6-69   |

|             | Program switching instruction                | Switching between main and subprogram                                                                            | 6-70 to 6-82   |

|             | Refresh instruction                          | Link refresh, partial refresh execution                                                                          | 6-83 to 6-90   |

|             | Logical operation instruction                | Logical operation such as logical sum and logical product                                                        | 7-2 to 7-21    |

|             | Rotation instruction                         | Rotation of specified data                                                                                       | 7-22 to 7-30   |

|             | Shift instruction                            | Shift of specified data                                                                                          | 7-31 to 7-39   |

|             | Data processing instruction                  | Data processing such as 16-bit data search, decode, and encode                                                   | 7-40 to 7-58   |

|             | FIFO instruction                             | Read/write of FIFO table                                                                                         | 7-59 to 7-63   |

| Application | Buffer memory access instruction             | Data read/write with special function modules and remote terminals(A2C/A52G).                                    | 7-64 to 7-87   |

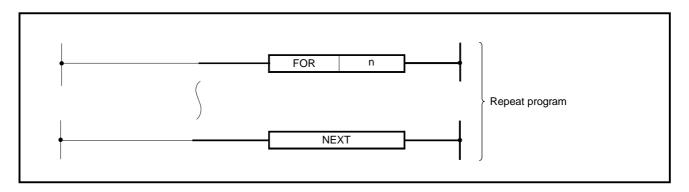

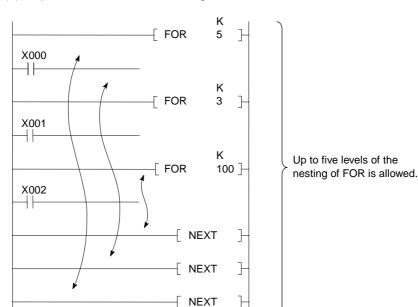

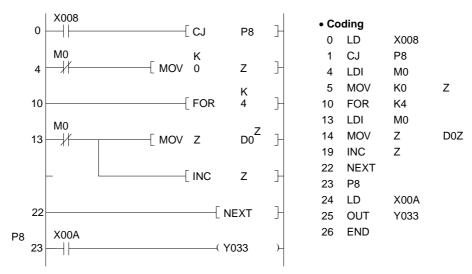

| instruction | FOR to NEXT instruction                      | Program repeated between FOR and NEXT instruction                                                                | 7-88 to 7-89   |

|             | Local, remote I/O station access instruction | Local, remote I/O station data read/write                                                                        | 7-90 to 7-103  |

|             | Display instruction                          | ASCII code print, character display on LED, etc.                                                                 | 7-104 to 7-120 |

|             | Others                                       | Instructions which are not included in the above classification, such as WDT reset, and set/reset of carry flag. | 7-121 to 7-138 |

|             | Instructions for servo programs              | Servo program execution and set value change                                                                     | 7-139 to 7-148 |

#### 2.2 Instruction List

## 2.2.1 Explanation for instructions lists

Instruction lists in Section 2.2.2 to 2.2.4 are in the following format.

**Table 2.2 Explanation for Instructions Lists**

| Classi-<br>fication       | Unit    | Instruction<br>Symbol | Symbol     | Contents of Processing        | Execu-<br>tion Con-<br>dition | Number * | Index | Subset | А   | pplicable CPU | Page |

|---------------------------|---------|-----------------------|------------|-------------------------------|-------------------------------|----------|-------|--------|-----|---------------|------|

|                           |         | +                     | + S D      | $(D)+(S){\rightarrow}(D)$     |                               | 5        | •     | •      | 0   |               | 6-10 |

|                           |         | +P                    | — +P S D — | (D)+(S)→(D)                   |                               | 5        | •     | •      | 0   |               | 6-10 |

|                           |         | +                     | + S1 S2 D  | $(S1) + (S2) \rightarrow (D)$ |                               | 7        | •     | •      | 0   |               | 6-10 |

| BIN<br>16-bit<br>addition | 16 bits | +P                    |            |                               |                               | 7        | •     | •      | 0   |               | 6-10 |

| /subtrac                  | 16      | -                     |            |                               |                               | 5        | •     | •      | 0   |               | 6-10 |

|                           |         | -P                    | — P S D    | $(D) - (S) \to (D)$           |                               | 5        | •     | •      | 0   |               | 6-10 |

|                           |         | -                     |            | (64) (62) . (D)               |                               | 7        | •     | •      | 0   |               | 6-10 |

|                           |         | +P                    |            | (S1) - (S2) → (D)             |                               | 7        | •     | •      | 0   |               | 6-10 |

| 1                         | 1       | 1                     | <b>↑</b>   | <u> </u>                      | 1                             | 1        | 1     | 1      | 1   |               | 1    |

| 1)                        | 2)      | 3)                    | 4)         | 5)                            | 6)                            | 7)       | 8)    | 9)     | 10) |               | 11)  |

## Explanation

- 1)..... Classifies the instructions by applications.

- 2)..... Indicates the unit of processing at the execution of instruction.

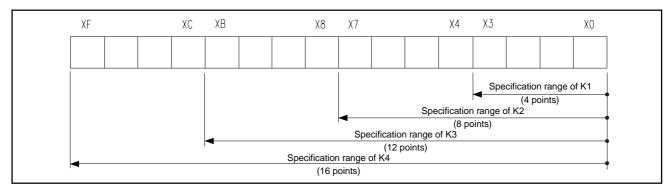

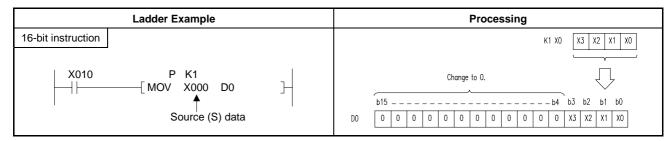

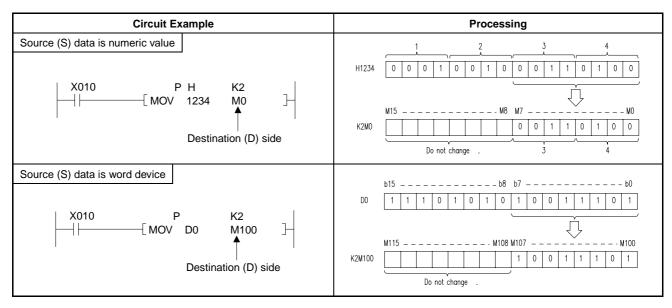

| Unit of<br>Processing | Device          | Number of Points                     |

|-----------------------|-----------------|--------------------------------------|

| 16 bits               | X,Y,M,L,F,B     | Max. 16 points in units of 4 points. |

| 10 bits               | T,C,D,W,R,A,Z,V | 1 point                              |

| 32 bits               | X,Y,M,L,F,B     | Max. 32 points In units of 4 points  |

| 32 DIIS               | T,C,D,W,R,A0,Z  | 2 Points                             |

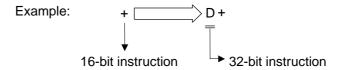

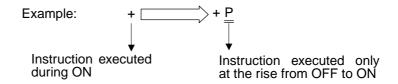

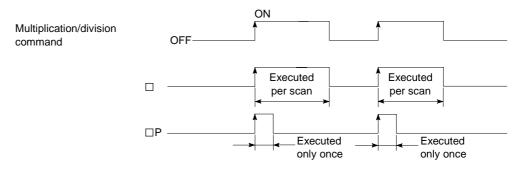

3)..... Indicates the instruction symbol used for the program. The instruction symbol is shown on a 16-bit instruction basis. The symbols of a 32-bit instruction and an instruction executed only at the rise from OFF to ON are as indicated below:

32-bit instruction......D is added to the head of instruction.

Instruction executed only at the rise from OFF to ON......P is added to the end of instruction.

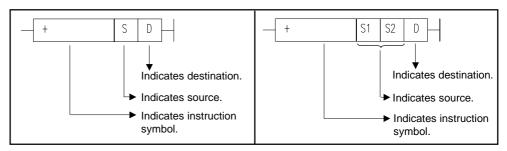

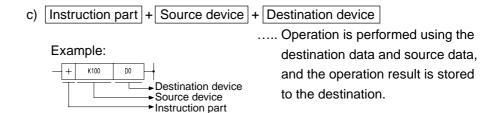

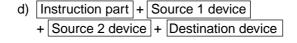

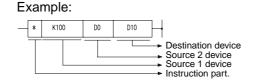

4)..... Indicates the symbol diagram in the circuit.

Fig. 2.1 Symbol Representations in Ladder

Destination: Indicates the destination of data after operation.

Source: Stores data before operation.

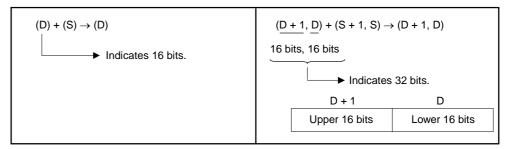

5)..... Indicates the processing of each instruction.

Fig. 2.2 Processing of Each Instruction

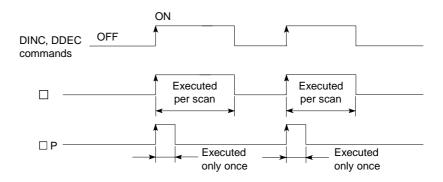

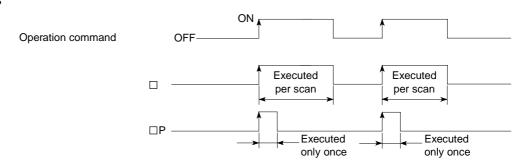

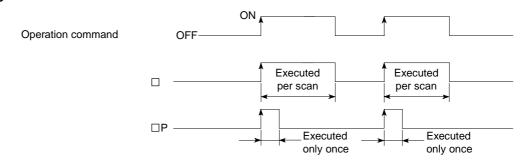

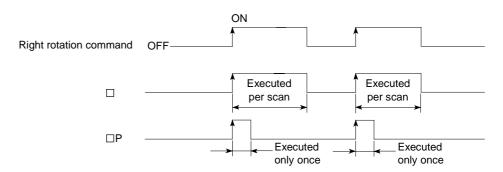

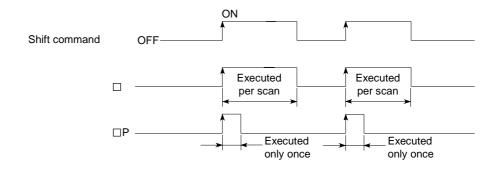

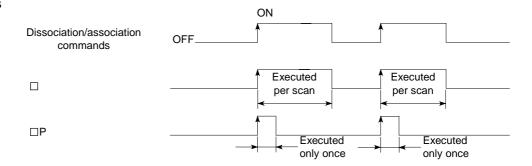

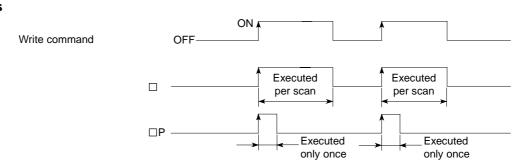

6).....Indicates the execution condition of each instruction and details are as described below:

| Symbol   | Execution Condition                                                                                                                                                                                                                                                                     |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No entry | Instruction which is always executed regardless of ON/OFF of the preceding condition. If the preceding condition is OFF, that instruction executes an OFF processing.                                                                                                                   |

|          | Instruction which is executed during ON. Executes instruction only while the preceding condition of that instruction is on. When the preceding condition is off, that instruction is not executed and not processed.                                                                    |

|          | Instruction which is executed once during ON. Executes instruction only at the positive transition of the preceding condition of instruction, i.e. the condition changes from off to on. Thereafter, even if the condition is on, that instruction is not executed and not processed.   |

|          | Instruction which is executed once during OFF. Executes instruction only at the negative transition of the preceding condition of instruction, i.e. the condition changes from on to off. Thereafter, even is the condition is off, that instruction is not executed and not processed. |

7)..... Indicates the number of steps of each instruction. The number of steps, which change depending on conditions, is indicated in two stages. For details, refer to each instruction.

#### **POINT**

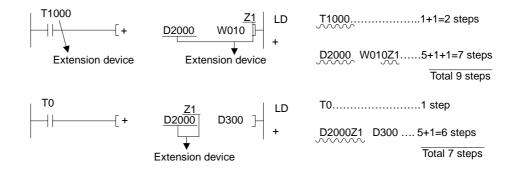

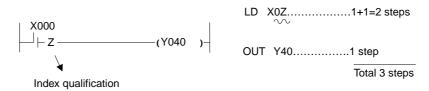

If extension devices are used or index qualification is performed with bit devices in the case of the instructions which need device specification for the AnA, A2AS, AnU, QCPU-A (A Mode) and A2USH board, the number of steps increases. Refer to Section 3.8.1 for details.

- 8)..... The mark indicates that the instruction can be indexed (Z, V).

The ▲ mark indicates that the instruction can be indexed with the AnA.

- The ▲ mark indicates that the instruction can be indexed with the AnA, A2AS, AnU, QCPU-A (A Mode) and A2USH board only.

- 9).....The mark indicates that the instruction is a subset instruction.

- The ▲ mark indicates that the subset processing can be performed with the A3H, A3M, AnA, A2AS, AnU, QCPU-A (A Mode) and A2USH board only.

- 10)... Indicates applicable CPU.

- The O mark indicates that it is applicable to all types of CPUs.

- The  $\triangle$  mark indicates that it is applicable to some types of CPUs.

- The mark indicates that it is applicable to specific CPUs.

- 11)....Indicates a page which explains each instruction.

#### 2.2.2 Sequence instructions

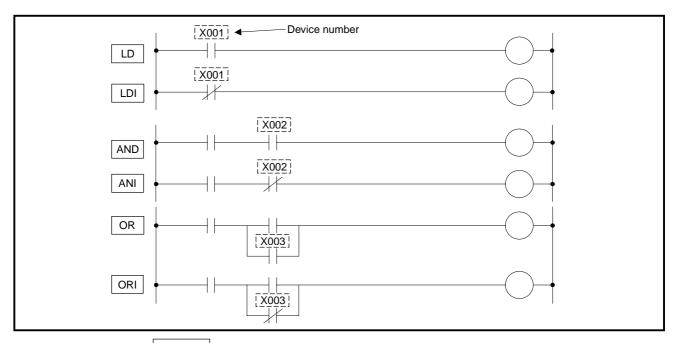

#### (1) Contact instructions

**Table 2.3 Contact Instructions**

| Classi-<br>fication | Unit | Instruction<br>Symbol | Symbol | Contents of Processing                                   | Execu-<br>tion Con-<br>dition | Number _*<br>of steps | Index          | Subset | Applicable CPU | Page |

|---------------------|------|-----------------------|--------|----------------------------------------------------------|-------------------------------|-----------------------|----------------|--------|----------------|------|

|                     |      | LD                    | H      | Logical operation start (NO contact operation start)     |                               | 1                     | *2<br><b>^</b> |        | 0              | 5-2  |

|                     |      | LDI                   |        | Logical NOT operation start (NC contact operation start) |                               | 1                     | *2<br>▲        |        | 0              | 5-2  |

| Contact             |      | AND                   | HH     | Logical product (NO contact series connection)           |                               | 1                     | *2<br><b>^</b> |        | 0              | 5-2  |

| Contact             |      | ANI                   | +      | Logical product NOT (NC contact series connection)       |                               | 1                     | *2<br><b>^</b> |        | 0              | 5-2  |

|                     |      | OR                    | ЧН     | Logical add (NO contact parallel connection)             |                               | 1                     | *2<br>▲        |        | 0              | 5-2  |

|                     |      | ORI                   | 4      | Logical add NOT (NC contact parallel connection)         |                               | 1                     | *2<br><b>≜</b> |        | 0              | 5-2  |

#### (2) Connection instructions

**Table 2.4 Connection Instructions**

| Classi-<br>flcation | Unit | Instruction<br>Symbol | Symbol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Contents of Processing                                     | Execu-<br>tion Con-<br>dition | Number of steps | mdex | Subset | Applicable CPU | Page |

|---------------------|------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-------------------------------|-----------------|------|--------|----------------|------|

|                     |      | ANB                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ANDs logical blocks. (Series connection of blocks)         |                               | 1               |      |        | 0              | 5-5  |

|                     |      | ORB                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Ors logical blocks.<br>(Parallel connection of blocks)     |                               | 1               |      |        | 0              | 5-5  |

| Connec-<br>tion     | -    | MPS                   | MPS CONTROL OF THE PROPERTY OF | Stores the operation result.                               |                               | 1               |      |        | 0              | 5-9  |

|                     |      | MRD                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Reads the operation result from MPS                        |                               | 1               |      |        | 0              | 5-9  |

|                     |      | MPP                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Reads the operation result from MPS and clears the result. |                               | 1               |      |        | 0              | 5-9  |

<sup>\*1:</sup> For the number of steps when extension devices are used or when index qualification is performed to bit devices for AnA, A2AS, AnU, QCPU-A (A Mode) and A2USH board, refer to Section 3.8.1.

<sup>\*2:</sup> The ▲ mark in the Index column indicates that index qualification can be performed with the AnA, A2AS, AnU, QCPU-A (A Mode) and A2USH board only.

<sup>\*3:</sup> The ▲ mark in the Subset column indicates that subset processing can be performed with the A3H, A3M, AnA, A2AS, AnU, QCPU-A (A Mode) and A2USH board only.

#### (3) Output instructions

**Table 2.5 Output instructions**

| Classi-<br>fication | Unit | Instruction<br>Symbol | Symbol        | Contents of Processing                                                   | Execu-<br>tion Con-<br>dition | Number 1* | xəpul          | Subset |   | Applicable CPU                                                                            | Page |

|---------------------|------|-----------------------|---------------|--------------------------------------------------------------------------|-------------------------------|-----------|----------------|--------|---|-------------------------------------------------------------------------------------------|------|

|                     |      | OUT                   | $\rightarrow$ | Device output                                                            |                               | 3         | *2<br>▲        |        | 0 |                                                                                           | 5-14 |

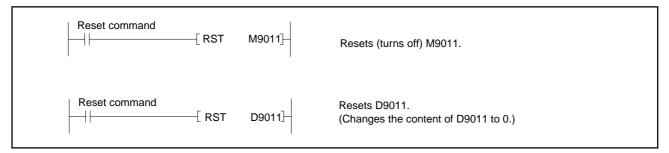

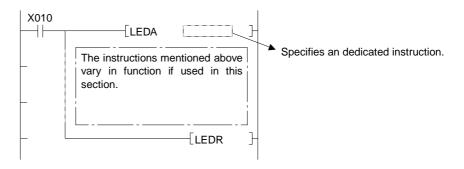

|                     |      | SET                   | — SET D       | Device set                                                               | *                             | 3         | *2<br>▲        |        | 0 |                                                                                           | 5-19 |